## DESIGN, ANALYSIS AND EXPERIMENTAL VERIFICATION OF CENTER-POINT-CLAMPED AC-AC CONVERTER

by

Pankaj Kumar Bhowmik

A thesis submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

Charlotte

2015

Approved by:

Dr. Madhav Manjrekar

Dr. Robert Cox

Dr. Badrul Chowdhury

©2015 Pankaj Kumar Bhowmik ALL RIGHTS RESERVED

#### ABSTRACT

## PANKAJ KUMAR BHOWMIK. Design, analysis and experimental verification of Center Point Clamped AC-AC Converter. (Under the direction of Dr. MADHAV MANJREKAR)

With the increasing use of electronic loads by the consumers, the utilities are facing more and more power quality issues. The advancement in semiconductor industry has led to introduction of power electronic devices as solutions to the power quality issues. But the implementation of these devices at utility scale voltage still remains challenging due to lack of power semiconductor devices rated at utility scale voltages. This thesis proposes a novel topology of power converter that uses semiconductor devices rated at about half the magnitude of utility scale voltage. This novel converter topology would help realizing a power electronic converter for utility scale voltages with easily available semiconductor devices that are rated at half the utility scale voltages.

This thesis investigates a center point clamped ac-ac topology for direct ac-ac power conversion. This converter topology introduces a unique methodology to clamp the voltage to the mid-point of the input transformer thus reducing the voltage blocking requirements on the bi-directional switches employed in such direct ac-ac converter. This thesis also discusses the considerations that are taken into account while designing an input filter for Center-Point-Clamped AC-AC Converter. The switched mode regulators due to their switching action feed in unwanted harmonic currents to the input side. These switching harmonics are attenuated by the designed input filter. But the addition of an input filter changes the transfer functions associated with the converter, which may degrade the performance of the converter and may even destabilize the system. The dynamic analysis of the Center-Point-Clamped AC-AC Converter with an input filter has

been discussed in the thesis. A feedback controller has been designed for closed loop control of the converter. Simulation results presented in the paper verify that the proposed converter offers high power transfer efficiency compared to conventional ac-dc-ac converters, and smaller output voltage ripple along with reduced voltage stress on the bidirectional switches when compared to other direct ac-ac converters. Also, it is seen that the designed input filter reduces the harmonic distortion of the input current, maintains the stability of the system as well as does not degrade the performance of the Center-Point-Clamped AC-AC converter. Experimental results demonstrating the Center-Point-Clamped mechanism of the converter as well as closed loop control of the AC-AC Converter are also presented in the paper.

#### ACKNOWLEDGEMENTS

I would like to express my gratitude towards my parents, my sister for believing in me and making it possible for me to follow my dream of pursuing higher education.

I would like to thank my advisor, Dr. Madhav Manjrekar, for his guidance and encouragement, without which, this thesis would not have been possible. His words can always inspire me and take me to higher level of thinking in my future endeavors.

It would be my duty to extend my gratitude to the committee members Dr. Robert Cox and Dr. Badrul Chowdhury for taking time to be on my committee and assess my work.

I am thankful to EPIC (Energy Production and Infrastructure Center) for its generous support.

Finally I am thankful to my lab mates, my friends and well-wishers who have always been there for me throughout the process.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                     | viii |

|-------------------------------------------------------------------------------------|------|

| LIST OF ABBREVIATIONS                                                               | xiv  |

| CHAPTER 1 : INTRODUCTION                                                            | 1    |

| 1.1. Introduction                                                                   | 1    |

| 1.2. Power Quality Issues in the Modern Utility Grid                                | 1    |

| 1.3. Comparison of Direct and Indirect AC-AC Converters                             | 2    |

| 1.4. Challenges and Thesis Motivation                                               | 3    |

| 1.5. Organization of Thesis                                                         | 4    |

| CHAPTER 2 : REVIEW OF AC-AC DIRECT POWER CONVERTERS                                 | 8    |

| 2.1. Introduction                                                                   | 8    |

| 2.2. Single Phase AC Chopper Circuit with Shunt Connected Bidirectional<br>Switches | 8    |

| 2.3. AC Chopper Circuit with Shunt Connected Bidirectional Switches                 | 9    |

| 2.4. Classical PWM Three Phase AC Chopper Circuit                                   | 12   |

| 2.5. Vector Switching Converter                                                     | 13   |

| 2.6. Matrix Converter                                                               | 14   |

| 2.7. Phase and Amplitude Controllable Transformer                                   | 16   |

| 2.8. Multilevel Direct AC Converter                                                 | 17   |

| CHAPTER 3 : CENTER-POINT-CLAMPED AC-AC BUCK CONVERTER                               | 20   |

| 3.1. Introduction                                                                   | 20   |

| 3.2. Evolution of Center-Point-Clamped AC-AC Converter                              | 21   |

| 3.3. Operating Principle of Center-Point-Clamped AC-AC Buck Converter               | 23   |

| 3.4. Methodology for Balancing Voltages across Input capacitors                     | 25   |

| CHAPTER 4 : CIRCUIT DESIGN OF CENTER-POINT-CLAMPED AC-AC<br>BUCK CONVERTER                       | 26 |

|--------------------------------------------------------------------------------------------------|----|

| 4.1. Introduction                                                                                | 26 |

| 4.2. Circuit Description                                                                         | 26 |

| 4.3. Power Circuit Design                                                                        | 27 |

| CHAPTER 5 : DYNAMIC ANALYSIS OF CENTER-POINT-CLAMPED<br>AC-AC BUCK CONVERTER                     | 37 |

| 5.1. Introduction                                                                                | 37 |

| 5.2. Circuit Description                                                                         | 37 |

| 5.3. State Space Equations                                                                       | 38 |

| 5.4. Dynamic Analysis                                                                            | 39 |

| CHAPTER 6 : CONTROLLER DESIGN FOR CLOSED LOOP CONTROL<br>OF CENTER-POINT-CLAMPED AC-AC CONVERTER | 60 |

| 6.1. Introduction                                                                                | 60 |

| 6.2. Circuit Description                                                                         | 60 |

| 6.3. Compensator Design                                                                          | 61 |

| CHAPTER 7 : INPUT FILTER CONSIDERATIONS FOR CENTER-POINT-<br>CLAMPED AC-AC CONVERTER             | 64 |

| 7.1. Introduction                                                                                | 64 |

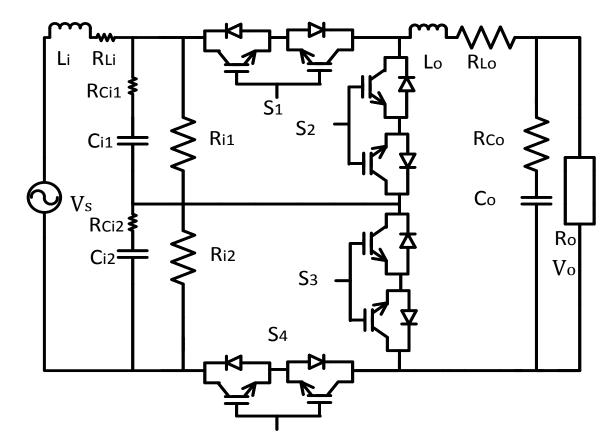

| 7.2. Modified Center-Point-Clamped AC-AC Converter Circuit                                       | 65 |

| 7.3. Description of Modified Center-Point-Clamped AC-AC Buck Converter<br>Circuit                | 66 |

| 7.4. Dynamic Analysis of Modified Center-Point-Clamped AC-AC Buck Converter                      | 66 |

| 7.5. Input Filter Considerations for Center-Point-Clamped AC-AC Converter<br>Circuit             | 77 |

vii

|                                                                    | viii |

|--------------------------------------------------------------------|------|

| CHAPTER 8 : SIMULATION RESULTS                                     | 85   |

| 8.1. Introduction                                                  | 85   |

| 8.2. Matlab-Simulink Model of Center-Point-Clamped AC-AC Converter | 86   |

| 8.3. Operational Simulation Results                                | 88   |

| 8.4. Open Loop Simulation Results                                  | 92   |

| 8.5. Closed Loop Simulation Results                                | 96   |

| CHAPTER 9 : EXPERIMENTAL RESULTS                                   | 103  |

| 9.1. Introduction                                                  | 103  |

| 9.2. Experimental Set-up Description                               | 104  |

| 9.3. Operational Experimental Results                              | 110  |

| 9.4. Open Loop Experimental Results                                | 114  |

| 9.5. Closed Loop Experimental Results                              | 119  |

| CHAPTER 10 : FAMILY OF CENTER-POINT-CLAMPED AC-AC<br>CONVERTERS    | 124  |

| 10.1. Introduction                                                 | 124  |

| 10.2. Center-Point-Clamped Direct AC-AC Buck Converter             | 125  |

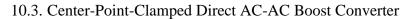

| 10.3. Center-Point-Clamped Direct AC-AC Boost Converter            | 128  |

| 10.4. Center-Point-Clamped Direct AC-AC Buck-Boost Converter       | 131  |

| 10.5. Center-Point-Clamped Direct AC-AC Ćuk Converter              | 134  |

| CHAPTER 11 : CONCLUSIONS                                           | 138  |

| REFERENCES                                                         | 140  |

## LIST OF FIGURES

| FIGURE 2 | 2.1: Simplified circuit schematic of the single phase of original ac chopper circuit with shunt connected bidirectional switch.              | 8  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 2 | 2.2: Simplified circuit schematic of the single phase of full ac chopper circuit with series and shunt connected bidirectional switches.     | 10 |

| FIGURE 2 | 2.3: Simplified circuit schematic of three-phase AC chopper with six bidirectional switches realized by twelve bipolar junction transistors. | 11 |

| FIGURE 2 | 2.4: Simplified circuit schematic of three-phase AC chopper circuit realized with six insulated gate bipolar transistors.                    | 12 |

| FIGURE 2 | 2.5: Simplified circuit schematic of Vector Switching Converter (VeSC).                                                                      | 13 |

| FIGURE 2 | 2.6: Simplified circuit schematic of a three phase to three phase matrix converter                                                           | 15 |

| FIGURE 2 | 2.7: Simplified circuit schematic of a Phase Amplitude Controllable<br>Transformer                                                           | 17 |

| FIGURE 2 | 2.8: Simplified circuit schematic of multilevel ac-ac converter.                                                                             | 18 |

| FIGURE 3 | 1: Simplified circuit schematics showing evolution of Center-Point-<br>Clamped AC-AC Converter.                                              | 21 |

| FIGURE 3 | 2.2: Simplified circuit schematic of an ac-ac converter.                                                                                     | 21 |

| FIGURE 3 | 3.3: Simplified circuit schematic of single phase center point clamped ac-ac converter.                                                      | 22 |

| FIGURE 3 | 3.4: Simplified circuit schematic of single phase center point clamped ac-ac converter.                                                      | 24 |

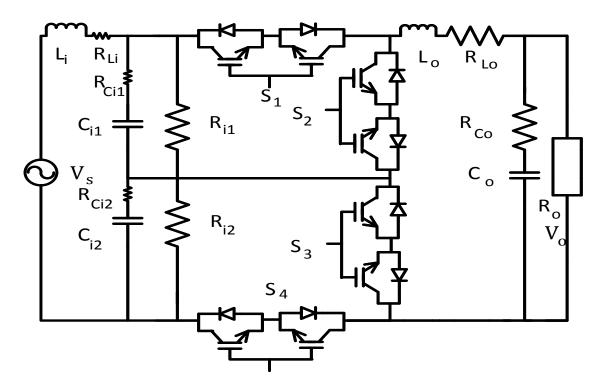

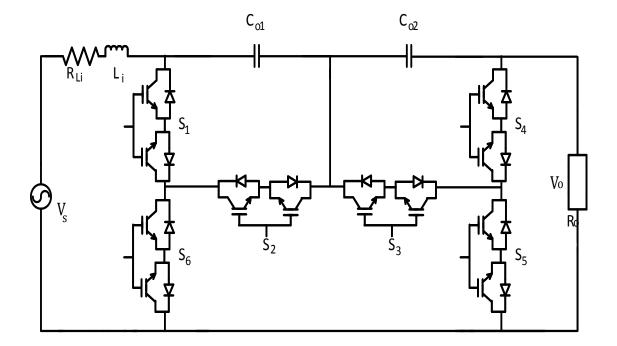

| FIGURE 4 | .1: Simplified circuit schematic of a single phase of center-point-<br>clamped ac-ac converter.                                              | 26 |

| FIGURE 4 | .2: Equivalent circuit of center-point-clamped ac-ac converter in interval $T_{1.}$                                                          | 28 |

| FIGURE 4 | .3: Equivalent circuit of center-point-clamped ac-ac converter in interval T <sub>2</sub> .                                                  | 29 |

| FIGURE 4 | .4: Equivalent circuit of center-point-clamped ac-ac converter in interval $T_1$ .                                                           | 32 |

|          |                                                                                                                                              |    |

| FIGURE 4.5: Equivalent circuit of center-point-clamped ac-ac converter in interval $T_2$ .                          | x<br>33 |

|---------------------------------------------------------------------------------------------------------------------|---------|

| FIGURE 5.1: Simplified circuit schematic of a single phase of center-point-<br>clamped ac-ac converter.             | 37      |

| FIGURE 5.2: Equivalent circuits of a center-point-clamped ac-ac converter in interval $T_1$ .                       | 39      |

| FIGURE 5.3: Equivalent circuit of a center-point-clamped ac-ac converter in interval $T_2$ .                        | 41      |

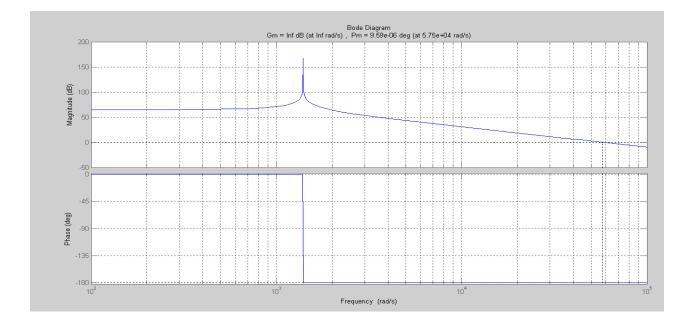

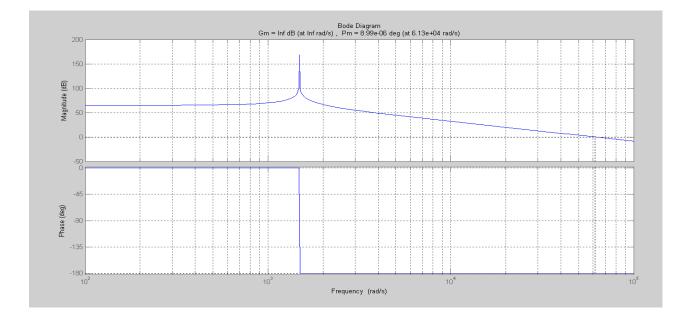

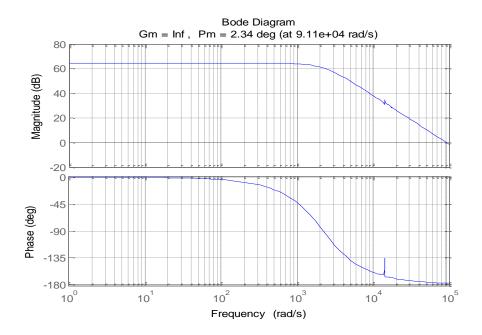

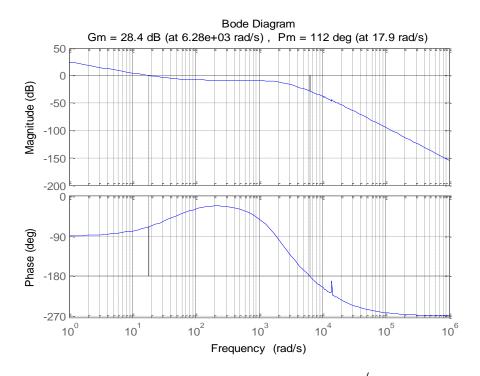

| FIGURE 5.4: Magnitude and phase plots of transfer function, $G_d$ for output voltage range 0 to $v_{in}/2$ .        | 48      |

| FIGURE 5.5: Magnitude and phase plots of transfer function, $G_v$ for output voltage range 0 to $v_{in}/2$ .        | 49      |

| FIGURE 5.6: Equivalent circuit of a center-point-clamped ac-ac converter in interval $T_1$ .                        | 49      |

| FIGURE 5.7: Equivalent circuits of a center-point-clamped ac-ac converter in interval T <sub>2</sub> .              | 51      |

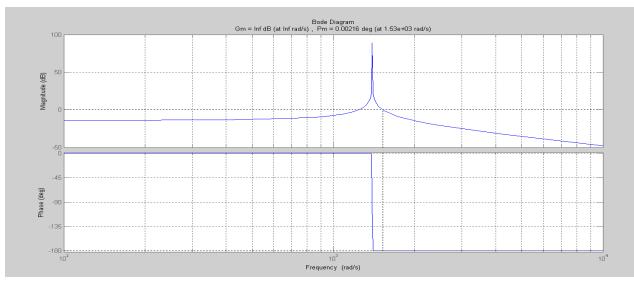

| FIGURE 5.8: Magnitude and phase plots of transfer function, $G_d$ for output voltage range $v_{in}/2$ to $v_{in}$ . | 58      |

| FIGURE 5.9: Magnitude and phase plots of transfer function, $G_v$ for output voltage range $v_{in}/2$ to $v_{in}$ . | 59      |

| FIGURE 6.1: Simplified circuit schematic of a single phase of center-point-<br>clamped ac-ac converter.             | 60      |

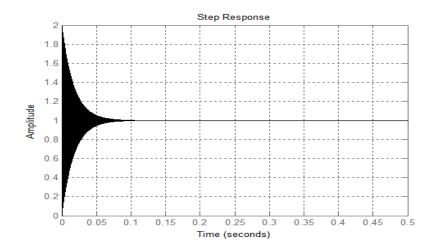

| FIGURE 6.2: Step response plot of uncompensated converter output voltage to duty cycle transfer function, $G_d$ .   | 62      |

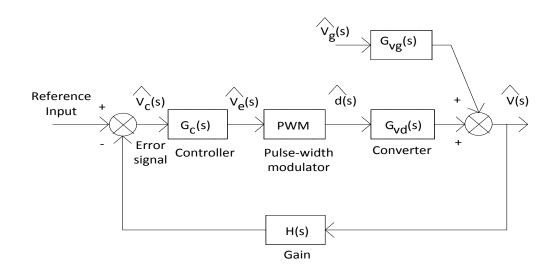

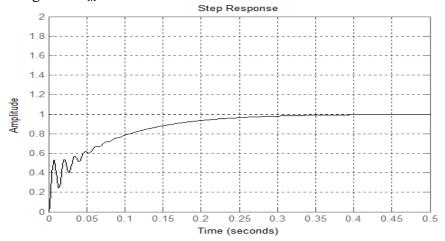

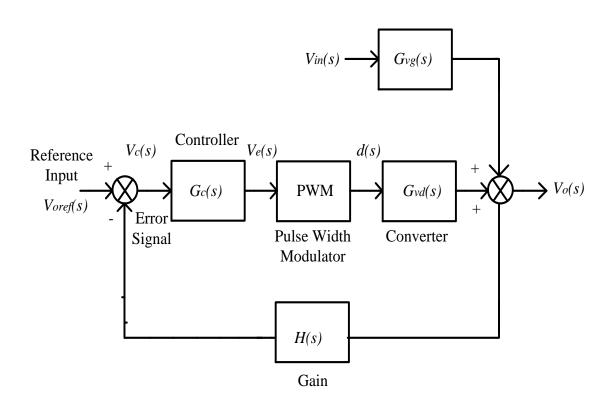

| FIGURE 6.3: Control block diagram of center-point-clamped ac-ac converter.                                          | 62      |

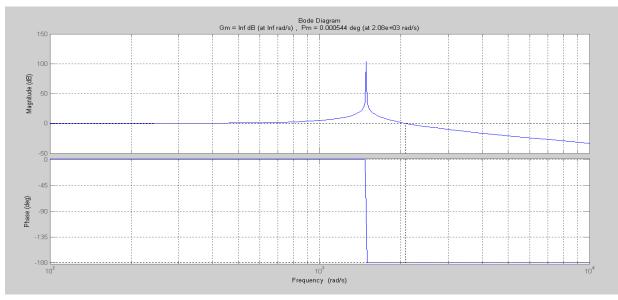

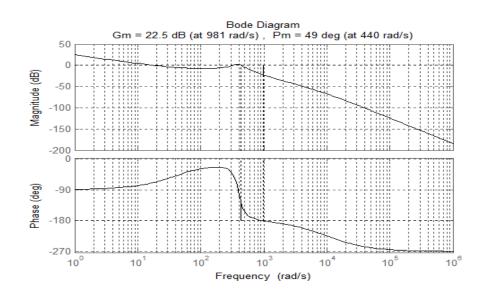

| FIGURE 6.4: Magnitude and phase plots of transfer function, $G_d * G_c$ for output voltage range 0 to $v_{in}$ .    | 63      |

| FIGURE 6.5: Step response plot of transfer function, $G_d * G_c$ for output voltage range 0 to $v_{in}$ .           | 63      |

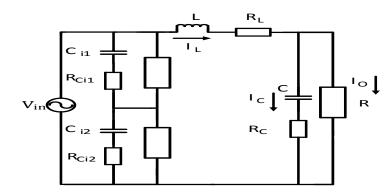

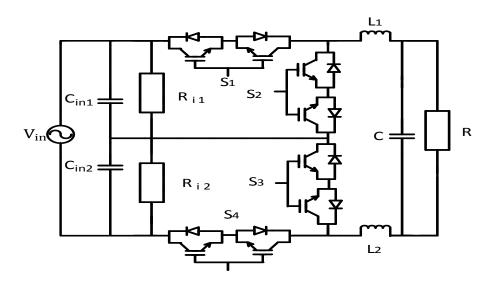

| FIGURE 7.1: Simplified circuit schematic of Center-Point-Clamped AC-AC converter with input filter.                 | 65      |

| FIGURE 7.2: Simplified circuit schematic of Center-Point-Clamped AC-AC converter with input filter.          | xi<br>77 |

|--------------------------------------------------------------------------------------------------------------|----------|

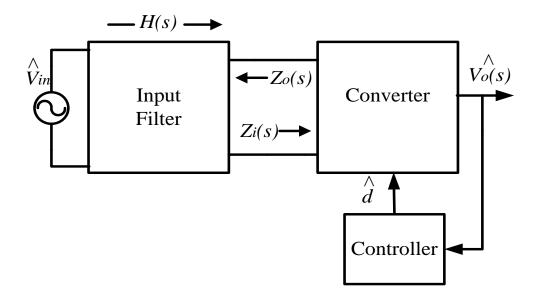

| FIGURE 7.3: Generalized block schematic of a converter with an input filter in addition to the output filter | 79       |

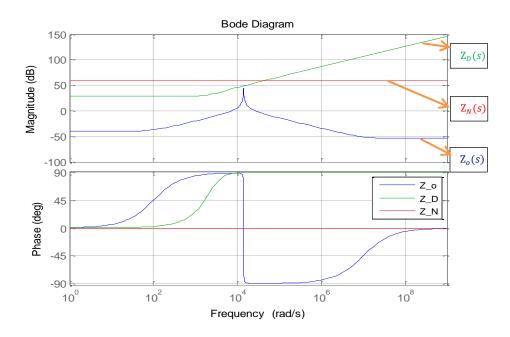

| FIGURE 7.4: Bode plots for $Z_o(s)$ , $Z_N(s)$ and $Z_D(s)$                                                  | 81       |

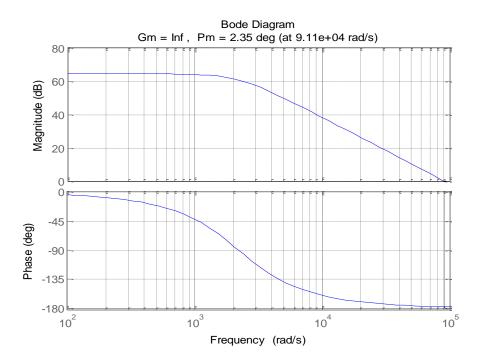

| FIGURE 7.5: Bode plot for $G_{vd}(s)$                                                                        | 82       |

| FIGURE 7.6: Bode plot of uncompensated transfer function, $G'_{vd}(s)$                                       | 82       |

| FIGURE 7.7: Bode plot of compensated transfer function $G'_{vd}(s) * G_c(s)$                                 | 83       |

| FIGURE 8.1: Simplified circuit schematic of Center-Point-Clamped AC-AC converter with input filter.          | 85       |

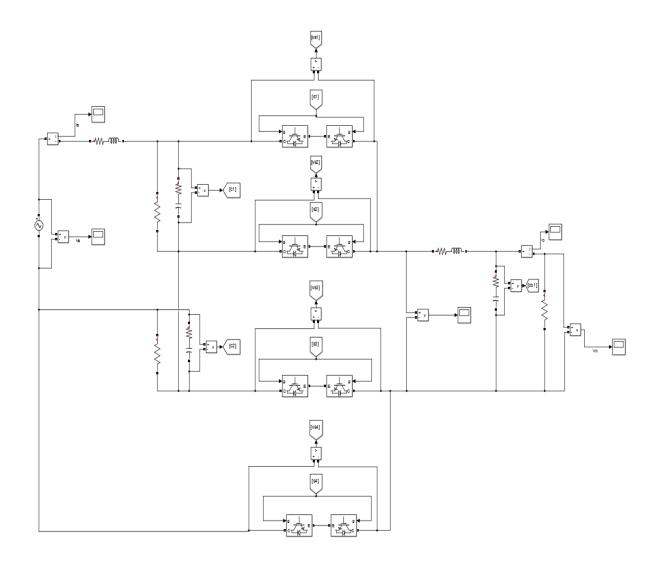

| FIGURE 8.2: Matlab-Simulink model of Center-Point-Clamped AC-AC converter with input filter.                 | 87       |

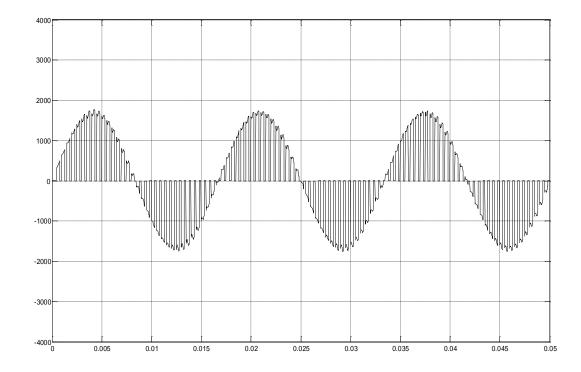

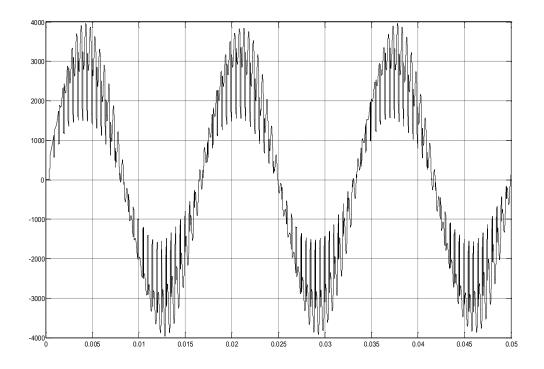

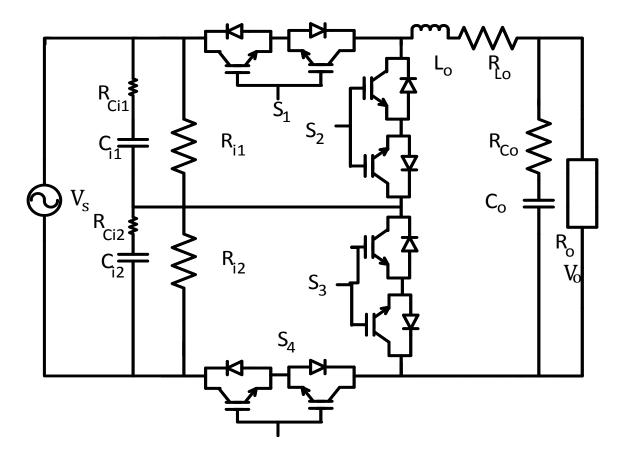

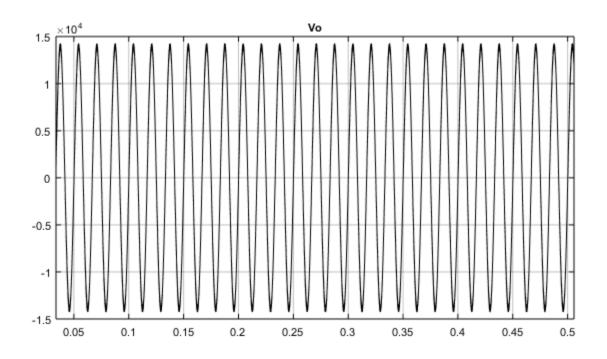

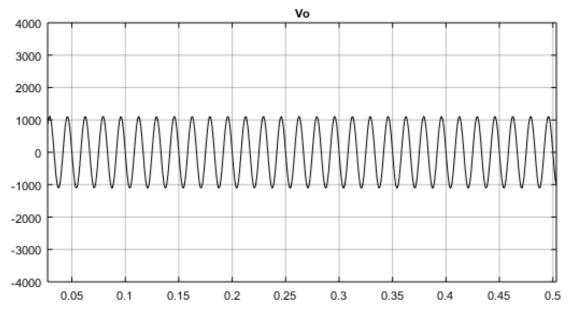

| FIGURE 8.3: Unfiltered Output Voltage waveforms when $v_{oref} = 0.3 v_{in}$                                 | 88       |

| FIGURE 8.4: Unfiltered Output Voltage waveforms when $v_{oref} = 0.8v_{in}$                                  | 89       |

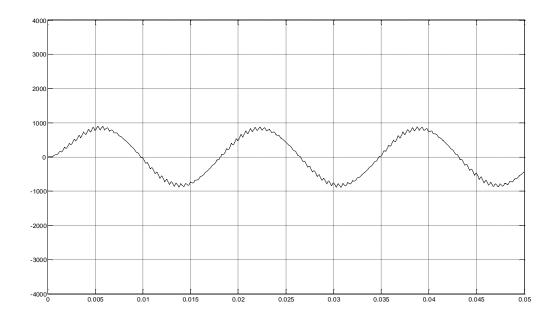

| FIGURE 8.5: Filtered Output Voltage waveforms when $v_{oref} = 0.8v_{in}$                                    | 89       |

| FIGURE 8.6: Filtered Output Voltage waveforms when $v_{oref} = 0.8v_{in}$                                    | 90       |

| FIGURE 8.7: Voltages across S2 and S3                                                                        | 91       |

| FIGURE 8.8: Voltages across $S_1$ and $S_4$                                                                  | 91       |

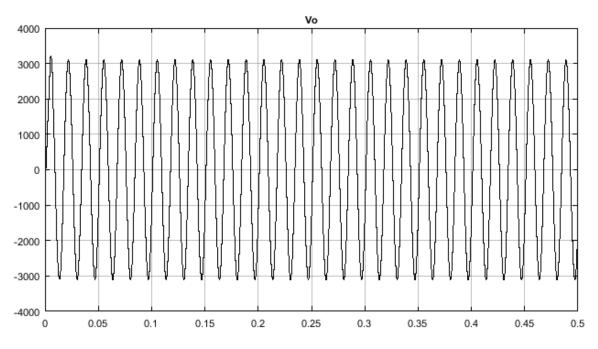

| FIGURE 8.9: Filtered output voltage waveform for D=0.25                                                      | 92       |

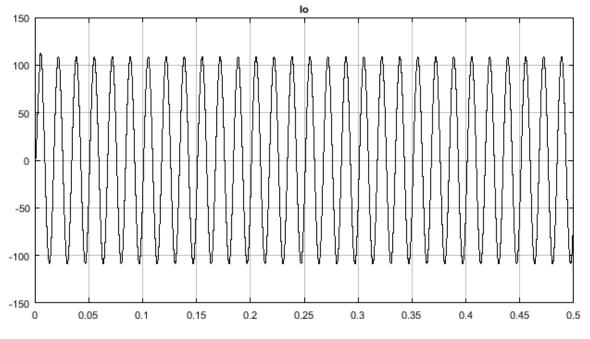

| FIGURE 8.10: Filtered output current waveform for D=0.25                                                     | 92       |

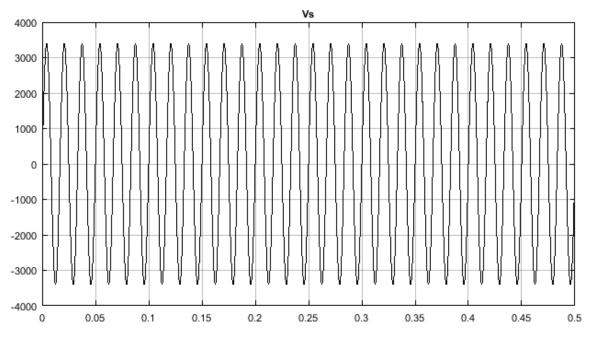

| FIGURE 8.11: Input source voltage waveform for D=0.25                                                        | 93       |

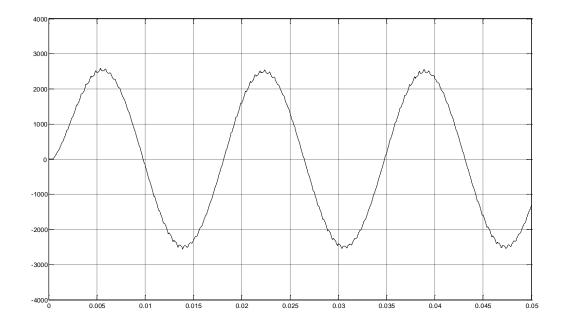

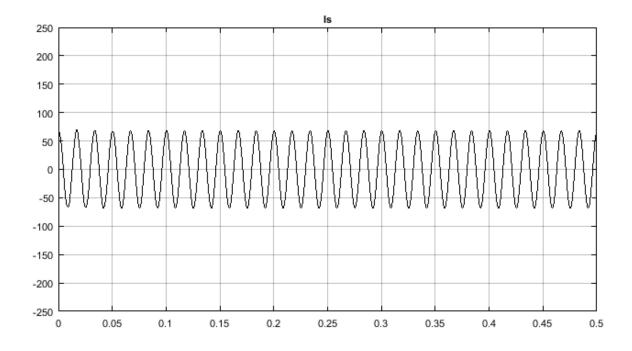

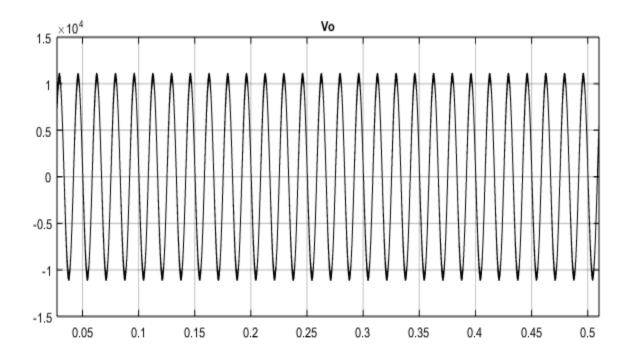

| FIGURE 8.12: Waveform of input current drawn from the source for D=0.25                                      | 93       |

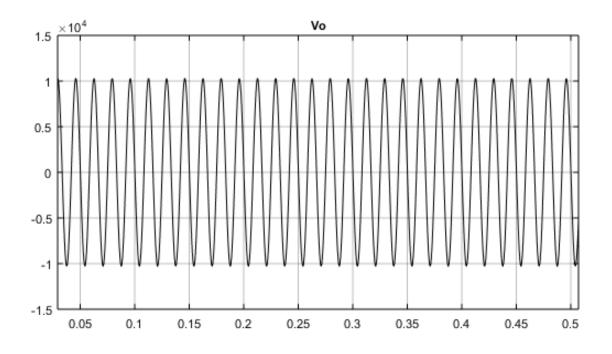

| FIGURE 8.13: Filtered output voltage waveform for D=0.75                                                     | 94       |

| FIGURE 8.14: Filtered output current waveform for D=0.75                                                     | 94       |

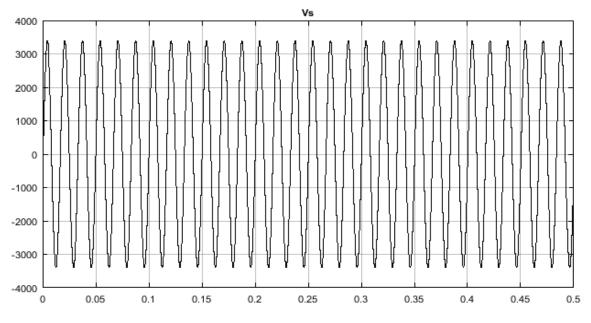

| FIGURE 8.15: Input source voltage waveform for D=0.75                                                        | 95       |

|                                                                                                                    | xii |

|--------------------------------------------------------------------------------------------------------------------|-----|

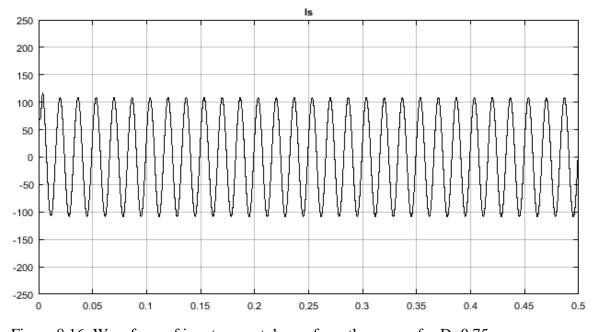

| FIGURE 8.16: Waveform of input current drawn from the source for D=0.75                                            | 95  |

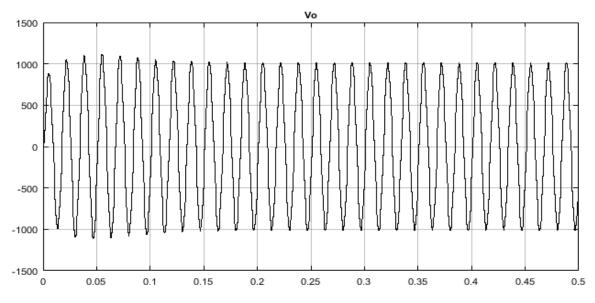

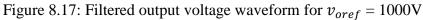

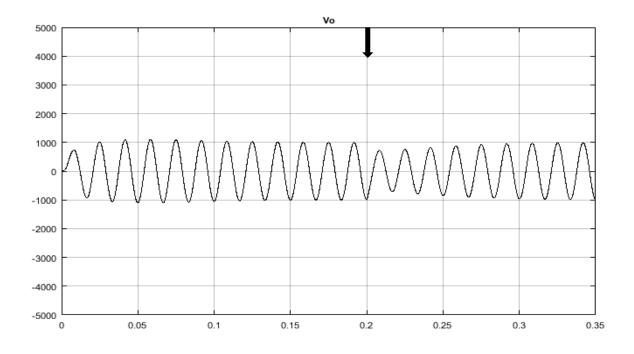

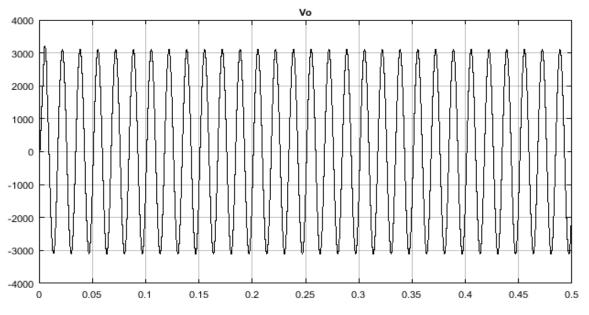

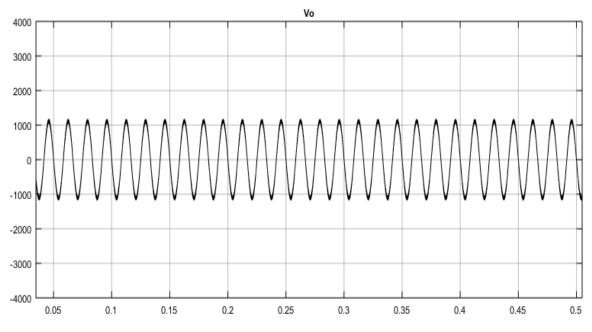

| FIGURE 8.17: Filtered output voltage waveform for $v_{oref} = 1000V$                                               | 96  |

| FIGURE 8.18: Filtered output voltage waveform for $v_{oref} = 3000$ V                                              | 96  |

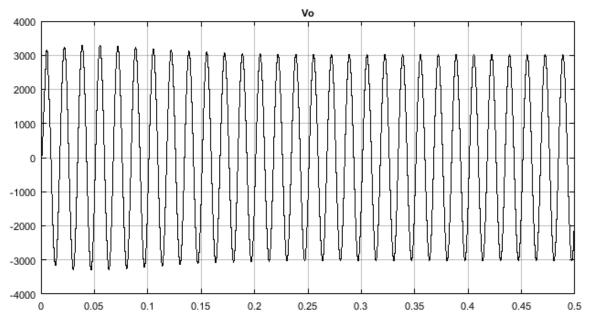

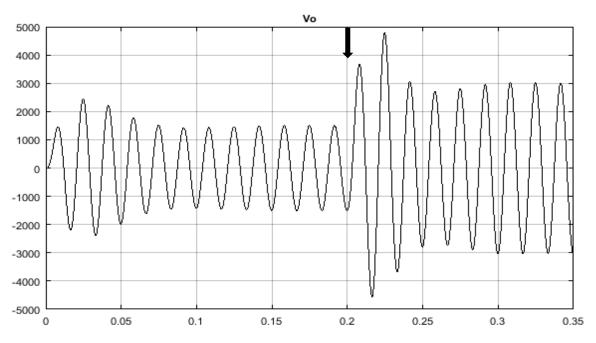

| FIGURE 8.19: Change of operating point within Region 1 (1000V to 1500V)                                            | 97  |

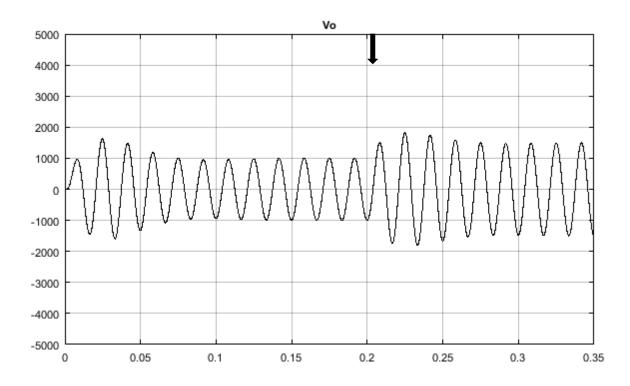

| FIGURE 8.20: Change of operating point within Region 2 (2500V to 3000V)                                            | 98  |

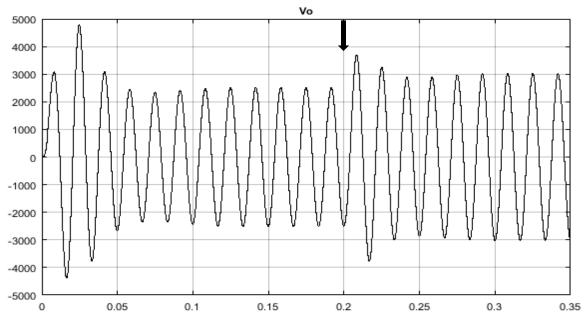

| FIGURE 8.21: Change of operating point from Region 1 (1500V) to Region 2 (3000V)                                   | 98  |

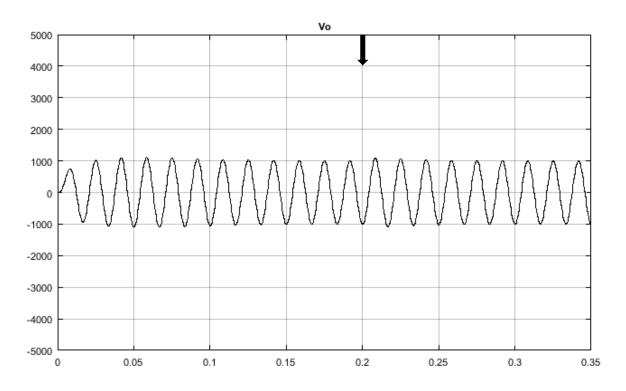

| FIGURE 8.22: Line regulation: performance during 10% increase in line voltage                                      | 99  |

| FIGURE 8.23: Line regulation: performance during 10% decrease in line voltage                                      | 100 |

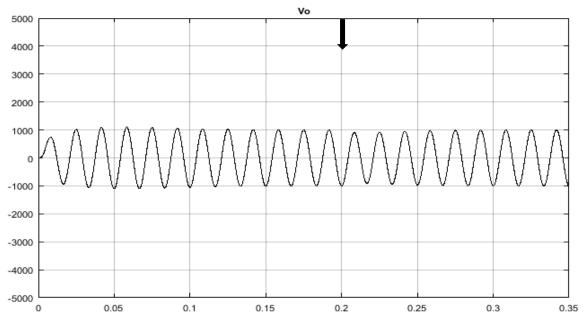

| FIGURE 8.24: Load regulation: performance during 50% decrease in load current                                      | 101 |

| FIGURE 8.25: Load regulation: performance during 50% decrease in load current                                      | 101 |

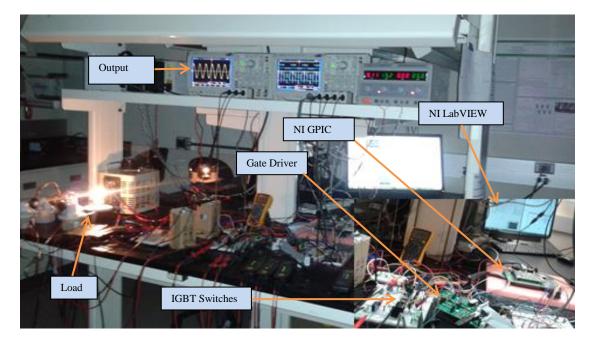

| FIGURE 9.1: Picture of experimental prototype in the laboratory                                                    | 104 |

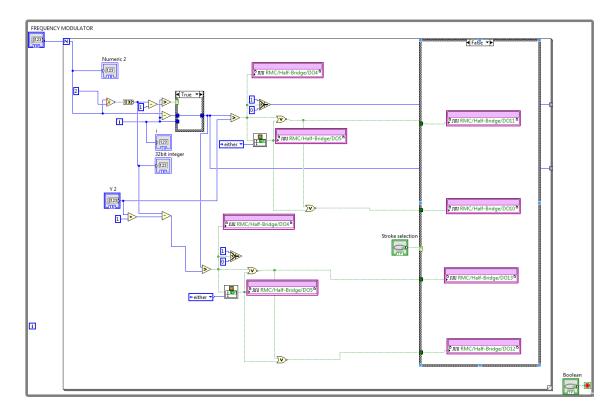

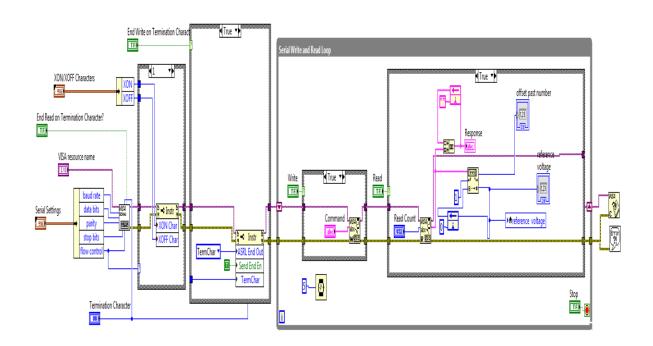

| FIGURE 9.2: Picture of LabVIEW VI Block Diagram window implementing the gate driver logic                          | 105 |

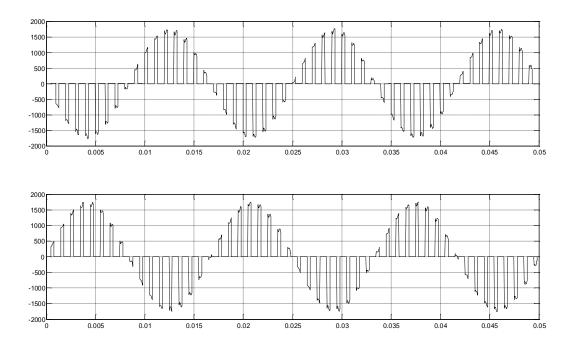

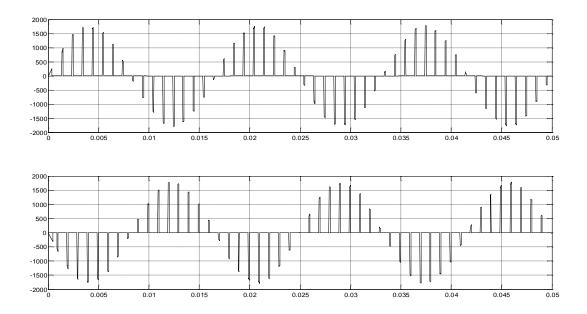

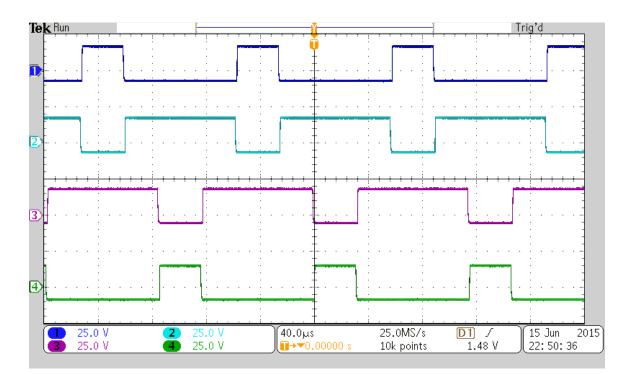

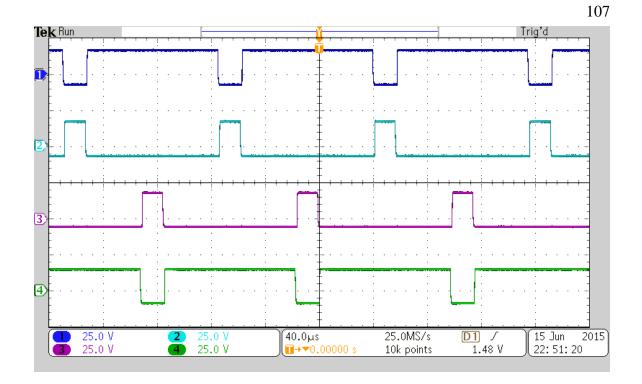

| FIGURE 9.3: Driver Logic Signal waveform for switches, $S_1$ , $S_2$ , $S_3$ , and $S_4$ when $v_{oref}=0.3v_{in}$ | 106 |

| FIGURE 9.4: Driver Logic Signal waveform for switches, $S_1$ , $S_2$ , $S_3$ , and $S_4$ when $v_{oref}=0.8v_{in}$ | 107 |

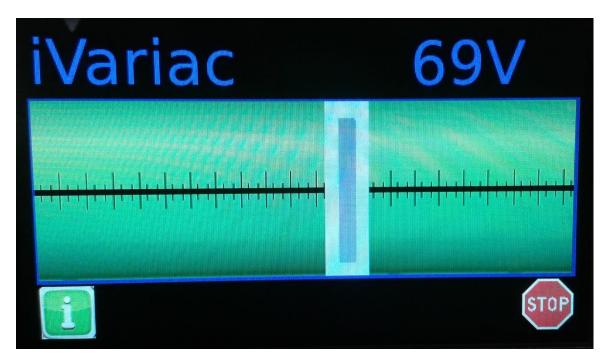

| FIGURE 9.5: User Interface for entering reference output voltage, $v_{oref}$ command input.                        | 107 |

| FIGURE 9.6: Picture of the LabVIEW VI sensing the reference output voltage, $v_{oref}$ from the slider input       | 108 |

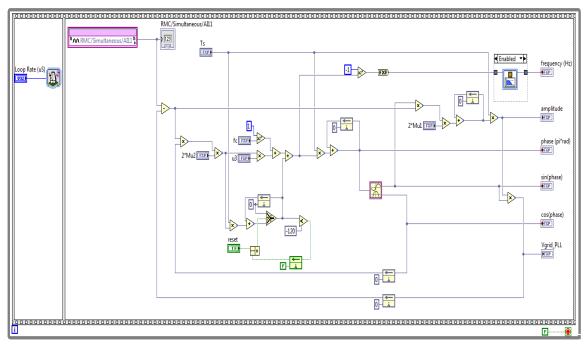

| FIGURE 9.7: Picture of the LabVIEW VI sensing output voltage, $v_o$ using Phase Locked Loop                        | 109 |

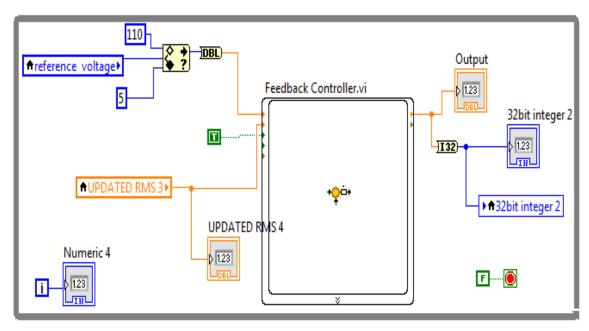

| FIGURE 9.8: Picture of the LabVIEW VI implementing the feedback controller                                         | 110 |

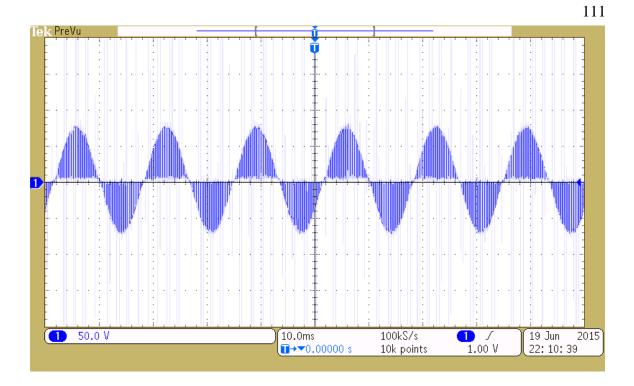

| FIGURE 9.9: Unfiltered Output Voltage waveforms when $v_{oref} = 0.3 v_{in}$                                       | 111 |

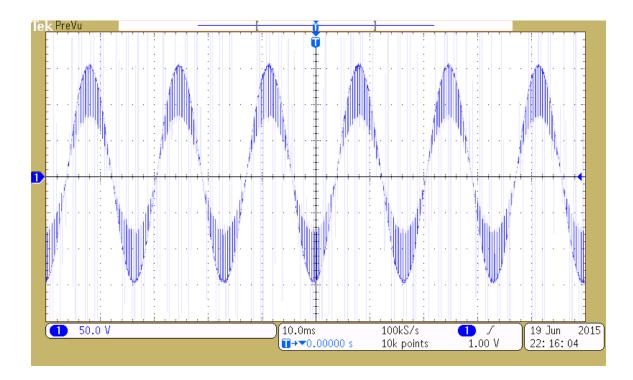

| FIGURE 9.10: Unfiltered Output Voltage waveforms when $v_{oref} = 0.8v_{in}$                           | xiii<br>111 |

|--------------------------------------------------------------------------------------------------------|-------------|

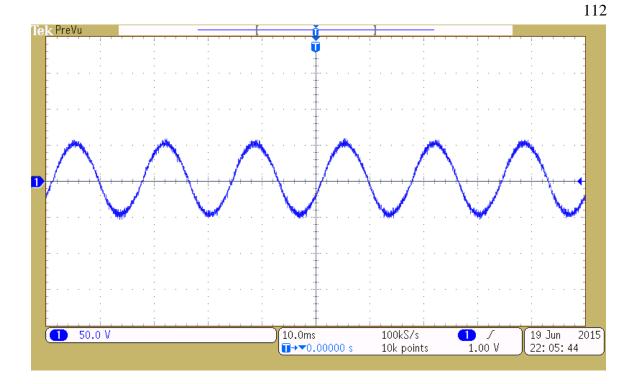

| FIGURE 9.11: Filtered Output Voltage waveforms when $v_{oref} = 0.3v_{in}$                             | 112         |

| FIGURE 9.12: Filtered Output Voltage waveforms when $v_{oref} = 0.8v_{in}$                             | 112         |

| FIGURE 9.13: Voltages across S2 and S3                                                                 | 113         |

| FIGURE 9.14: Voltages across $S_1$ and $S_4$                                                           | 114         |

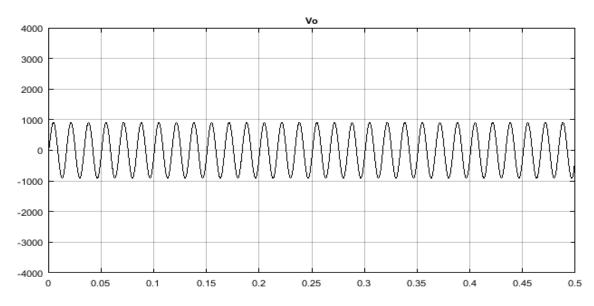

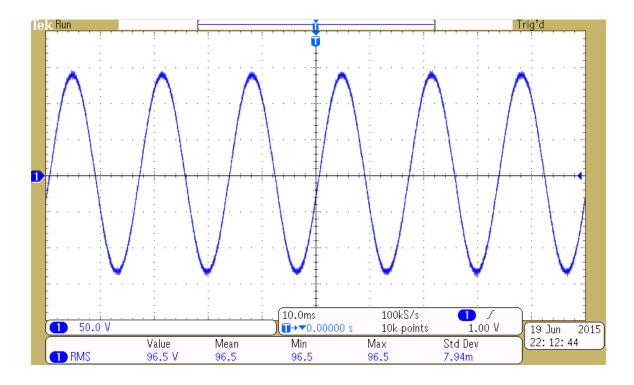

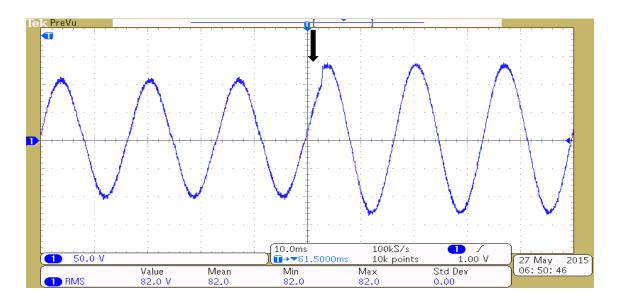

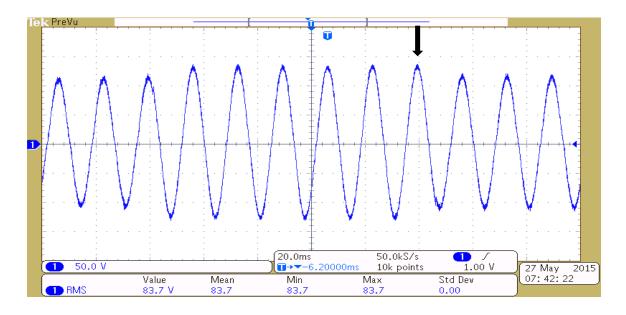

| FIGURE 9.15: Filtered output voltage waveform for D=0.25                                               | 115         |

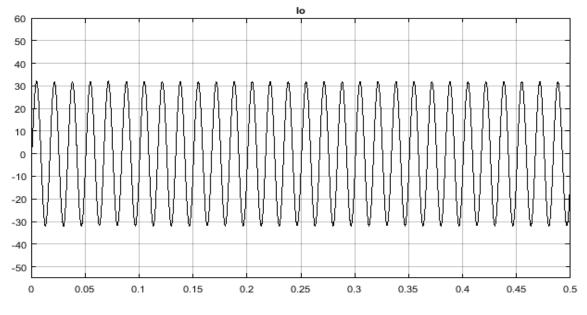

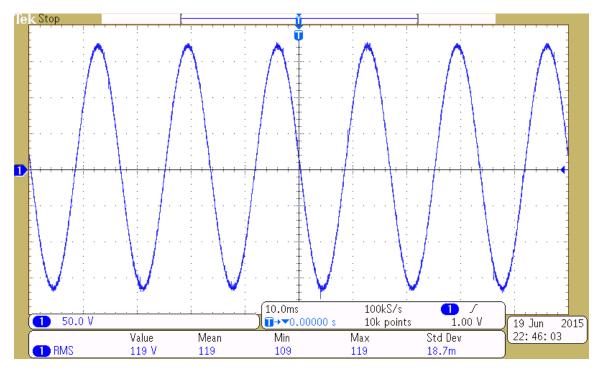

| FIGURE 9.16: Filtered output current waveform for D=0.25                                               | 115         |

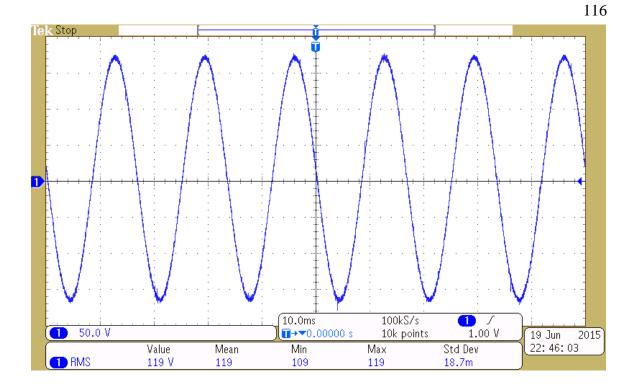

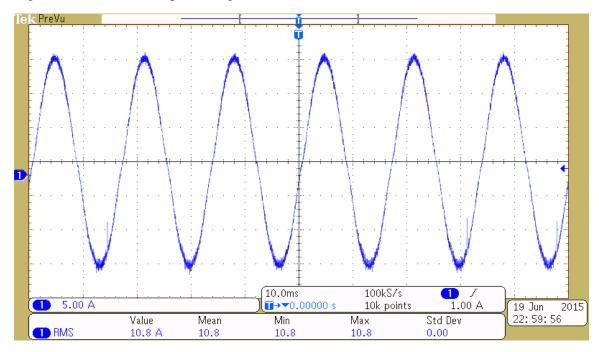

| FIGURE 9.17: Input source voltage waveform for D=0.25                                                  | 116         |

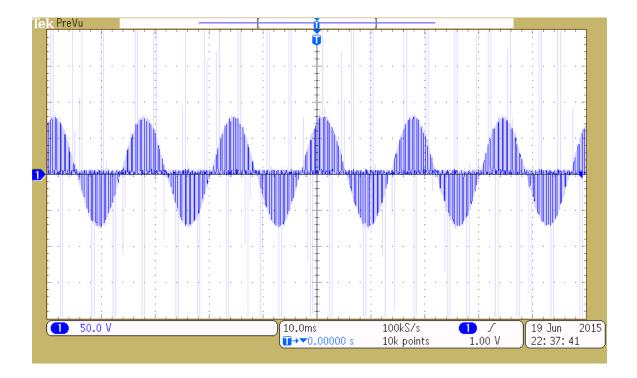

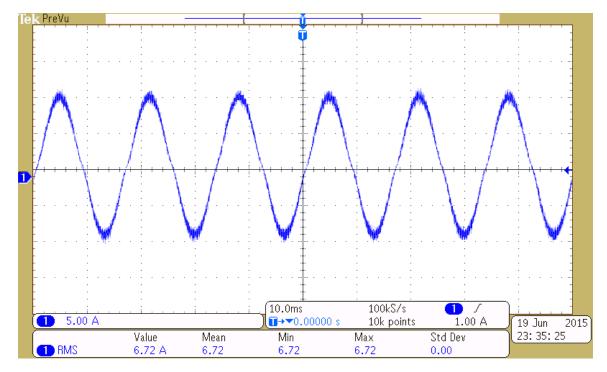

| FIGURE 9.18: Waveform of input current drawn from the source for D=0.25                                | 116         |

| FIGURE 9.19: Filtered output voltage waveform for D=0.75                                               | 117         |

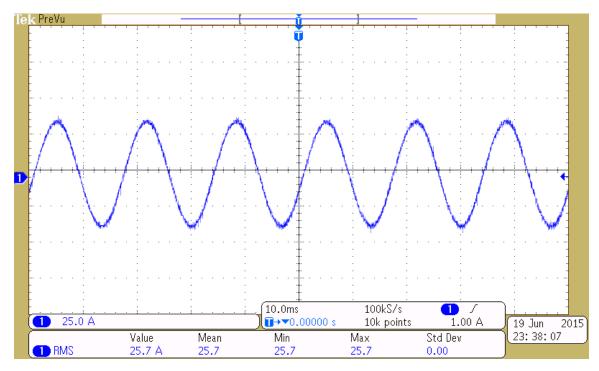

| FIGURE 9.20: Filtered output current waveform for D=0.75                                               | 117         |

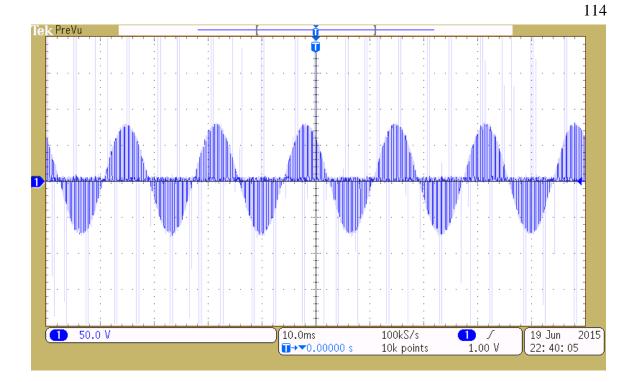

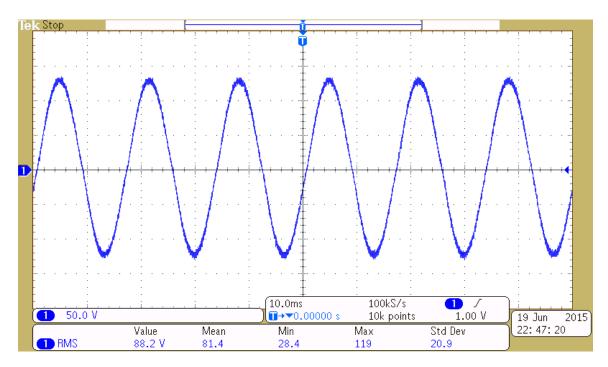

| FIGURE 9.21: Input source voltage waveform for D=0.75                                                  | 118         |

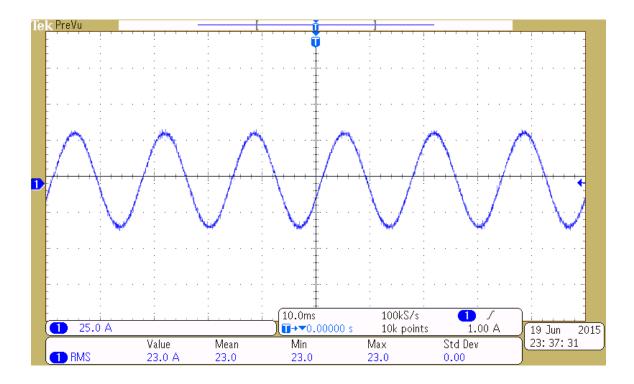

| FIGURE 9.22: Waveform of input current drawn from the source for D=0.75                                | 118         |

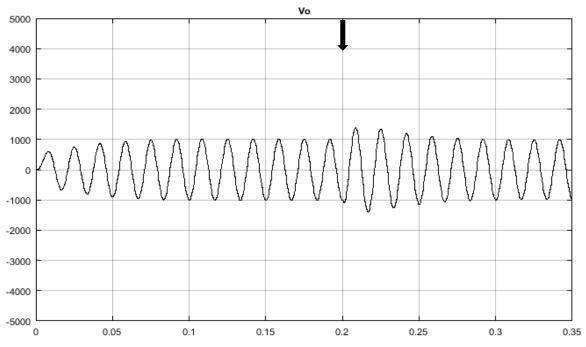

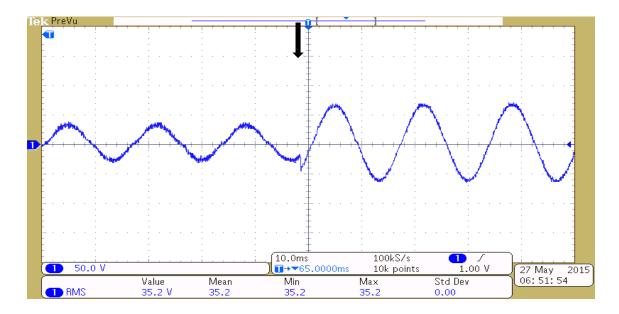

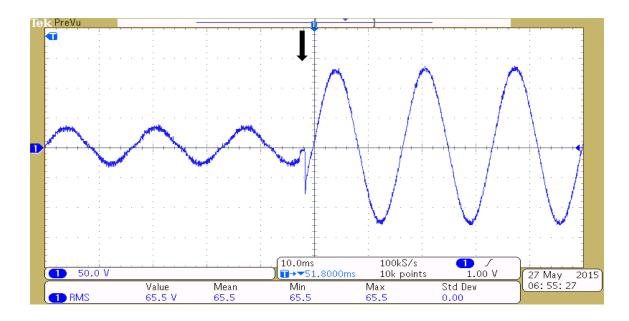

| FIGURE 9.23: Change of operating point within Region 1 (20V to 50V).                                   | 119         |

| FIGURE 9.24: Change of operating point within Region 2 (70V to 90V).                                   | 120         |

| FIGURE 9.25: Change of operating point from Region 1 (20V) to Region 2 (90V).                          | 120         |

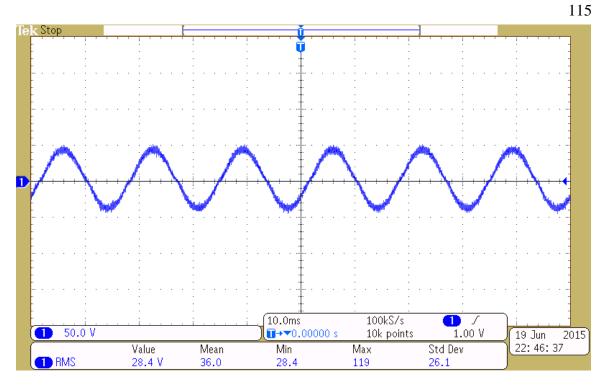

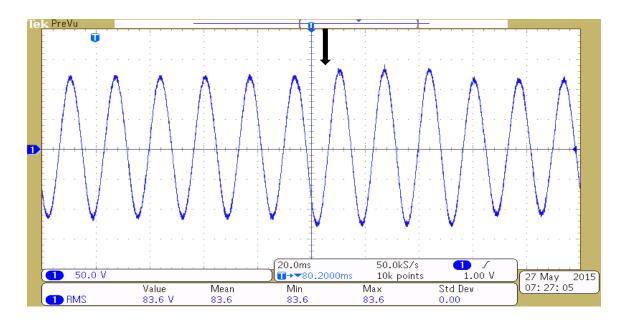

| FIGURE 9.26: Line regulation: performance during step increase in line voltage when $v_{oref} = 80$ V. | 121         |

| FIGURE 9.27: Line regulation: performance during step decrease in line voltage when $v_{oref} = 80$ V. | 121         |

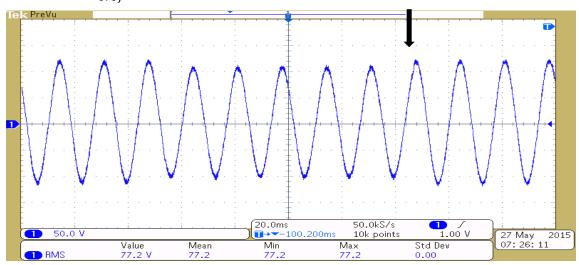

| FIGURE 9.28: Load regulation: performance during step decrease in load current when $v_{oref} = 80$ V. | 122         |

| FIGURE 9.29: Load regulation: performance during step increase in load current when $v_{oref} = 80$ V. | 123         |

| FIGURE 10.1: Simplified Circuit Schematic of a Center-Point-Clamped Direct                             | 125         |

AC-AC Buck Converter

| FIGURE 10.2: Filtered output voltage waveform for D=0.25                                                 | 126 |

|----------------------------------------------------------------------------------------------------------|-----|

| FIGURE 10.3: Filtered output voltage waveform for D=0.75                                                 | 127 |

| FIGURE 10.4: Simplified Circuit Schematic of a Center-Point-Clamped Direct<br>AC-AC Boost Converter      | 128 |

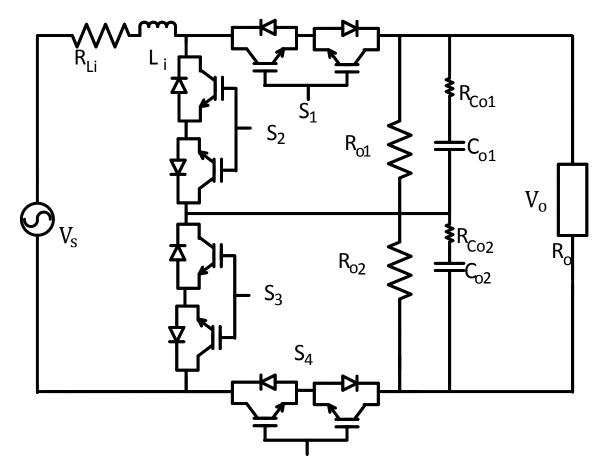

| FIGURE 10.5: Filtered output voltage waveform for D=0.25                                                 | 130 |

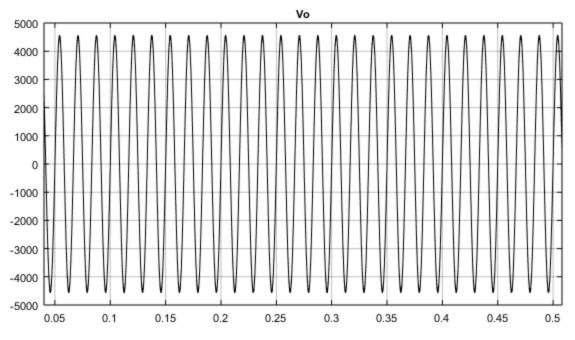

| FIGURE 10.6: Filtered output voltage waveform for D=0.75                                                 | 130 |

| FIGURE 10.7: Simplified Circuit Schematic of a Center-Point-Clamped Direct<br>AC-AC Buck-Boost Converter | 131 |

| FIGURE 10.8: Filtered output voltage waveform for D=0.25                                                 | 133 |

| FIGURE 10.9: Filtered output voltage waveform for D=0.75                                                 | 133 |

| FIGURE 10.10: Simplified Circuit Schematic of a Center-Point-Clamped Direct<br>AC-AC Ćuk Converter       | 134 |

| FIGURE 10.11: Filtered output voltage waveform for D=0.25                                                | 136 |

| FIGURE 10.12: Filtered output voltage waveform for D=0.75                                                | 136 |

xiv

# LIST OF ABBREVIATIONS

| BJT   | Bipolar Junction Transistor              |

|-------|------------------------------------------|

| IGBT  | Integrated Gate Bipolar Transistor       |

| SOA   | Safe Operating Area                      |

| PWM   | Pulse Width Modulation                   |

| VeSC  | Vector Switching Converter               |

| PACT  | Phase Amplitude Controllable Transformer |

| TACC  | Thin AC Converters                       |

| SISO  | Single Input/Single Output               |

| GUI   | Graphical User Interface                 |

| EMI   | Electro-Magnetic Interference            |

| NI    | National Instruments                     |

| GPIC  | General Purpose Inverter Controller      |

| VI    | Virtual Instrument                       |

| QML   | Query Mark-up Language                   |

| MSO   | Mixed Signal Oscilloscope                |

| FACTS | Flexible AC Transmission Systems         |

## **CHAPTER 1 : INTRODUCTION**

### 1.1. Introduction

This chapter presents a brief introduction and organization of the thesis. Importance of power control equipment to improve power quality is emphasized in Section 1.2. Section 1.3 presents the importance of direct ac-ac converters. Section 1.4 discusses the challenges faced when operating at high voltage and high power levels as well as the primary motivation for the thesis. The concluding section presents organization of the thesis.

#### 1.2. Power Quality Issues in the Modern Utility Grid

Increasing use of loads supplied by electronic power converters in industry has led to growing problems with reliability of the power supply. Computers, adjustable speed drives and automated manufacturing processes are very susceptible to voltage sags, spikes and power interruptions [1], [2]. The need for a reliable and high quality power supply has led to the increased adoption of electronic power conditioning devices and uninterruptible power supplies, which regulate voltages within acceptable tolerances [1], [15]-[17]. Another important issue affecting the modern utility grid is the addition of renewable energy sources to satisfy the surging energy demands. Penetration of renewable energy resources, while critical from the perspective of meeting increasing energy demands, adds to grid congestion and affects system operation [2]. Over the last few decades there has been a growing need for enhanced grid control capabilities

attributed to these issues. Advances in power semiconductor devices have made it possible for utilities to use a variety of power electronics based power control equipment to improve power quality. But the implementation of these power electronic solutions at utility scale voltages remain challenging as semiconductor devices at utility scale voltages are not readily available in the market. Also, these power electronic solutions are costly and less efficient, as they are quite complex. Thus, it may be noted that owing to high cost, complexity and poor reliability these solutions have seen minimal market penetration.

#### 1.3. Comparison of Direct and Indirect AC-AC Converters

The direct ac-ac converter is one of the candidates in realizing a low cost power quality solution with high system reliability [1], [2], [10], [11]. This direct ac-ac conversion is unlike an inverter-based ac-dc-ac converter where additional energy storage is required (in the form of a dc link capacitor). In an indirect ac-ac converter, the power conversion occurs in several stages, like ac power is rectified to dc power and then dc power is inverted to ac power. The intermediate stages in an indirect ac-ac converter involve additional energy storage capacitors. Although such indirect ac-ac converters are simple to control and are cost competitive, they suffer from disadvantages such as requirement of storage element, viz. capacitor, which are bulky in size. Also, the multiple stages in an indirect ac-ac converter often involve a number of active and passive devices, which reduces its efficiency as well as life span. On the other hand, direct ac-ac power converters, without energy storage elements offer advantages such as, single-stage power conversion, superior harmonic content, better efficiency and smaller footprint [2], [10], [11]. Although a number of direct ac-ac converter topologies have been reported in

literature, yet the implementation of these converters at utility scale voltages and power have been a critical issue due to lack of availability of semiconductor devices rated at utility level voltages and power.

#### 1.4. Challenges and Thesis Motivation

Operation of power conditioning systems such as direct ac-ac converters at high voltage and power levels requires semiconductor devices with high voltage blocking and high current carrying capabilities. Commercially available Insulated Gate Bipolar Transistors (IGBTs) rated up to 1700V/1200A that are low cost have been a workhorse for industrial applications operating at 480Vac [2]. These devices operate with relatively high switching frequencies. In order to operate direct ac-ac converter at higher voltage levels in the range of 4.16kV-13.8kV, it requires semiconductor devices rated at those higher voltage levels. As for instance, the phase-neutral peak voltage in a 4.16kV system is 3.4kV. To ensure that devices work reliably within their Safe Operating Area (SOA), it is required to employ either a 6.6kV IGBT or a series connection of two 3.3kV devices for this application. Because of lack of widely available 6.6kV devices, an alternative has been to employ series connection of 3.3kV IGBTs. This increases complexity and cost of system due to issues associated with static and dynamic voltage sharing of series connected IGBTs [2], [18]-[22]. It may be observed that as the voltage ratings of the semiconductor devices increase, the switch on resistance increases, thereby increasing the switching losses and reducing the efficiency of the semiconductor switch based power conditioning devices. An effective solution to all these challenges pertaining to construct a reliable and efficient power conditioning device has been proposed in this thesis in the form of a novel topology of direct ac-ac converter termed as Center-Point-Clamped AC-

AC Direct Power Converter. With the proposed center-point-clamped ac-ac converter topology, it has been shown that one can reliably construct an efficient power conditioning device for utility scale voltage and power ratings using semiconductor devices rated at half the utility scale voltages and power.

#### 1.5. Organization of Thesis

This section presents an overview of the organization of thesis as follows:

Chapter 1: Introduction

This chapter starts by describing the importance of power control equipment to improve power quality in Section 1.2. The advantages of direct ac-ac converters over traditional ac-dc-ac converters are briefly discussed in Section 1.3. The challenges faced at higher voltage and power levels leading to the thesis motivation are discussed in Sections 1.4. The organization of the thesis is presented in Section 1.5.

Chapter 2: Review of AC-AC Direct Power Converters

This chapter presents the evolution of different types of AC-AC Direct Power Converters. A brief overview of the chapter is presented in Section 2.1. The single phase ac chopper circuit with shunt connected bidirectional switches is discussed in Section 2.2. The single phase and three phase ac chopper circuit with shunt and series connected bidirectional switches are studied in Section 2.3. The three phase AC chopper circuit constituting classical model of Pulse Width Modulation (PWM) based converter topologies, viz. buck, boost, and buck-boost converter are analyzed in Section 2.4. The Vector Switching Converter topology for M sources and N loads is discussed in Section 2.5. A generalized model of matrix converter is examined in Section 2.6. The Phase and Amplitude Controllable Transformer and a multilevel topology of AC-AC converter are studied in Section 2.7 and Section 2.8 respectively.

Chapter 3: Center-Point-Clamped AC-AC Buck Converter

This chapter introduces the novel topology of Center-Point-Clamped AC-AC Buck Converter. The functional capability of Center-Point-Clamped AC-AC Buck Converter is presented in Section 3.1. The working principle of Center-Point-Clamped AC-AC Buck Converter along with its switching sequence is discussed in Section 3.2. The principle of voltage balancing across the input capacitors is analyzed in Section 3.3.

Chapter 4: Circuit Design of Center-Point-Clamped AC-AC Buck Converter

This chapter discusses the circuit design principles followed to derive the various circuit parameters for the Center-Point-Clamped AC-AC Buck Converter. The preface to the chapter is presented in Section 4.1. The simplified circuit schematic of the converter is described in Section 4.2. The design of the converter circuit parameters is analyzed in Section 4.3.

Chapter 5: Dynamic Analysis of Center-Point-Clamped AC-AC Buck Converter

This chapter examines the dynamic analysis of the Center-Point-Clamped AC-AC Buck Converter. A brief overview of the chapter is presented in Section 5.1. The simplified circuit schematic of the converter is described in Section 5.2. The state space equations for the converter are obtained in Section 5.3. The dynamic analysis of the converter transfer functions is presented in Section 5.4.

Chapter 6: Controller Design for closed loop control of Center-Point-Clamped AC-AC Converter This chapter deals with the design of a feedback controller for closed loop operation of the Center-Point-Clamped AC-AC Buck Converter. The motivation behind this chapter is mentioned in Section 6.1. The simplified circuit schematic of the converter is shown in Section 6.2. The design of the feedback controller has been analyzed in Section 6.3.

Chapter 7: Input Filter considerations for Center-Point-Clamped AC-AC Converter

This chapter examines the considerations that have to be taken care of while designing an input filter for the converter so that the unregulated input side power supply does not get affected due to harmonics generated by the switching action of the converter. A brief preface to the chapter is presented in Section 7.1. The modified simplified circuit schematic of the converter is presented and described in Section 7.2 and Section 7.3. The dynamic analysis of the modified converter circuit is presented in Section 7.4. The considerations for designing the input filter for the converter are analyzed in Section 7.5.

**Chapter 8: Simulation Results**

This chapter presents the simulation results verifying the efficacy of the Center-Point-Clamped AC-AC Buck Converter. An introduction to the chapter is provided in Section 8.1. The simulation model of the converter is presented in Section 8.2. The waveforms supporting the operating principle of the converter are analyzed in Section 8.3. The open loop and closed loop simulation results are presented in Section 8.4 and Section 8.5 respectively.

**Chapter 9: Experimental Results**

This chapter discusses the experimental results obtained from a laboratory prototype verifying the practical realization and efficacy of the Center-Point-Clamped AC-AC

Buck Converter. The objective of this chapter is shown in Section 9.1. The experimental set-up is discussed in Section 9.2. The experimental waveforms explaining the operating principle of the converter are presented in Section 9.3. The open loop and closed loop experimental results are presented in Section 9.4 and Section 9.5.

Chapter 10: Family of Center-Point-Clamped AC-AC Converters

This chapter starts by stating the advantages of the family of Center-Point-Clamped AC-AC Direct Power Converter in Section 10.1. The operating principles and the switching methodologies of family of Center-Point-Clamped AC-AC Converters, viz. buck converter, boost converter, buck-boost converter, Ćuk converter are presented in Sections 10.2, 10.3, 10.4, and 10.5 respectively.

Chapter 11: Conclusions

This chapter contains a brief summary of the overall thesis. It also highlights the arguments and solutions presented in the thesis.

## CHAPTER 2 : REVIEW OF AC-AC DIRECT POWER CONVERTERS

## 2.1. Introduction

A brief review of direct ac-ac converters has been presented in the following sections. Although a number of direct ac-ac converters have been reported in literature, selected topologies of converters that are more practical are discussed in the following sections.

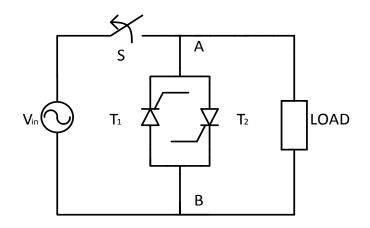

2.2. Single Phase Ac Chopper Circuit with Shunt Connected Bidirectional Switches One of the first appearances of ac chopper circuit can be traced back to 1968 when it was employed for load voltage regulation applications [3]. In this paper, a technique has been introduced, based on forced ignition and extinction of thyristor based switches for ac voltage regulation. A schematic circuit diagram of the proposed technique is shown in figure 2.1.

Figure 2.1: Simplified circuit schematic of the single phase of original ac chopper circuit with shunt connected bidirectional switch.

A simplified circuit schematic of one of the earliest known ac chopper circuit has been shown in figure 2.1. It has a switch S which is series with the load.  $\gamma$  is the switching period of the switch S. The switch S is closed during the time interval,  $\theta$  and opened during the rest of the switching time period, i.e. time interval  $\gamma - \theta$ . Thus, one cycle of the input voltage may be divided into integral multiples of the switching period. This technique is one of the fundamental PWM based ac voltage regulation applicable in resistive loads. However, it has inherent advantages in case of inductive loads and discontinuous load current as the circuit provides a means to discharge the magnetic energy stored in the inductor. During the half-cycle in which terminal A is at positive potential and S is switched off, thyristor,  $T_1$  is switched on and  $T_2$  is switched off. During the second half-cycle in which terminal B is at positive potential and S is switched on, thyristor,  $T_2$  is switched on and  $T_1$  is switched off. Thus, this methodology enables the prevention of exchange of reactive power between load and source owing to the discharge of magnetic energy near the load. The arrangement of thyristors  $T_1$  and  $T_2$  in back to back configuration acting as bidirectional switches is one of the earliest evidence of ac voltage regulation based on bidirectional switches that has been reported in the literature.

### 2.3. AC Chopper Circuit with Shunt Connected Bidirectional Switches

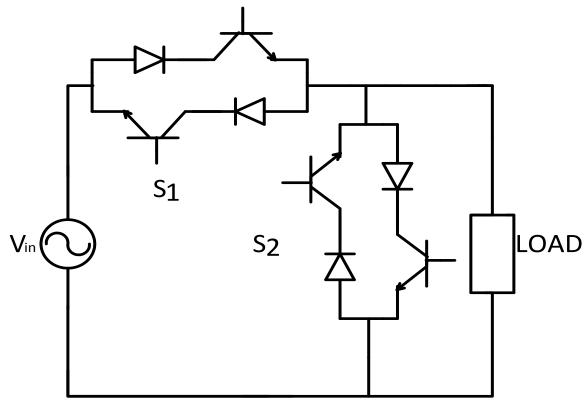

Extending the concept of ac voltage regulation further, a combination of shunt and series bidirectional switches realizing a full ac chopper circuit has been reported in [4] for power control applications.

Figure 2.2: Simplified circuit schematic of the single phase of full ac chopper circuit with series and shunt connected bidirectional switches.

The single phase version of ac chopper may be seen in figure 2.2. The bidirectional switches,  $S_1$  and  $S_2$  are closed and opened in a complementary fashion, thereby resulting in chopped ac voltage at the output. The fundamental or rms voltage can be regulated by varying the time ratio,  $\tau = t_{on} / (t_{on} + t_{off})$  of the chopping transistors, where  $t_{on}$  and  $t_{off}$  are the time duration when the switch is closed and opened respectively. In early years, one of the primary hurdles in widespread deployment of this technology was practical realization of a bidirectional switch using Bipolar Junction Transistor (BJT) based devices. A three-phase version of the ac chopper consisted of six bidirectional switches which required twelve BJTs as shown in figure 2.3 [4].

Figure 2.3: Simplified circuit schematic of three-phase AC chopper with six bidirectional switches realized by twelve bipolar junction transistors

The principles of single-phase full ac chopper circuit as in figure 2.2 may be extended to the three phase version as shown in figure 2.3. Since star and delta connected loads are mutually convertible, and the mode of operation is the same in either case, only a star connected load is shown in figure 2.3. The circuit consists of three BJT based bidirectional switches in series and three in shunt. The series switches either act as ac chopping switches in active mode or act as closed switches in the feedback mode. The shunt switches provide a current freewheeling path in active mode or serve as open switches if corresponding line voltage is positive.

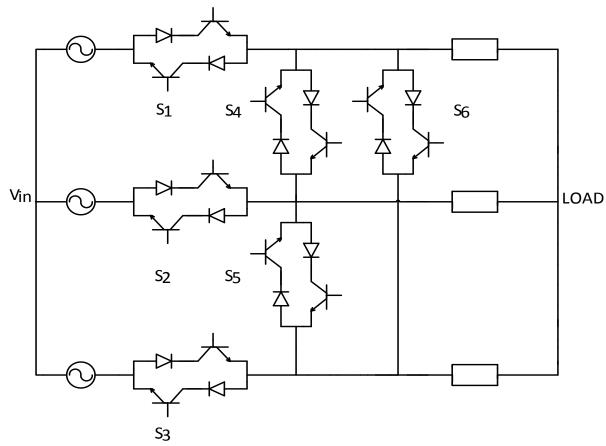

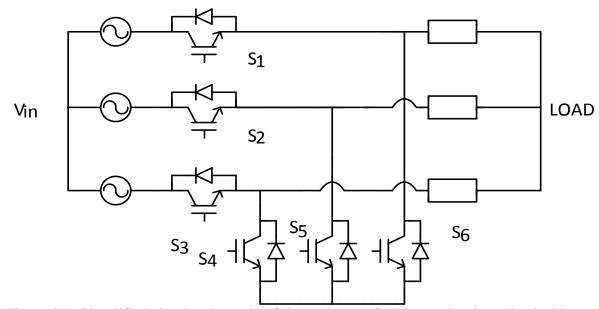

## 2.4. Classical PWM Three Phase AC Chopper Circuit

An equivalent three-phase ac chopper that employed six Integrated Gate Bipolar Transistors (IGBTs) was introduced in [5]. As may be seen from figure 2.4, this topology consists of three floated wye-connected shunt IGBTs which together with their anti-parallel diodes, form bidirectional switches between any two terminals.

Figure 2.4: Simplified circuit schematic of three-phase AC chopper circuit realized with six insulated gate bipolar transistors.

The three main modes of operation of the ac chopper shown in figure 2.4, are active mode, bypass mode and freewheeling mode. In the active mode of operation, the switches  $S_1$ ,  $S_2$ , and  $S_3$  are closed and the rest are opened. Thus, the input voltages appear across the load, while the three line currents are conducted by one or two top switches ( $S_1$ ,  $S_2$  and  $S_3$ ) and two or one diodes antiparallel to top switches. The bypass mode of operation is the transition mode from active mode to freewheeling mode of operation. In this mode, the input and output currents maintain continuity through snubber circuitry (bypass capacitors with parallel bleeding resistors connected in shunt with each line). In the

freewheeling mode of operation, the bottom switches ( $S_4$ ,  $S_5$  and  $S_6$ ) are turned on while the rest are turned off. Thus, the three load voltages and the three input line currents are zero, while the three load currents are conducted by one bottom switch and two bottom diodes or vice-versa. The fundamental concept of ac chopper (ac-ac buck converter) topology shown in figure 2.4 can be extended to other forms of switched mode power converters such as boost converter, buck-boost converter, Ćuk converter etc. and has been reported in [6] and [7].

## 2.5. Vector Switching Converter

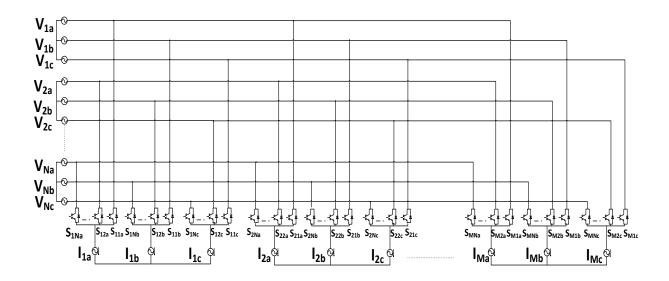

The converter shown in figure 2.4 that was originally conceived for a single source, single load system has been further generalized for N sources and M loads with a topology named Vector Switching Converter (VeSC) [8]. A simplified schematic of generalized three-phase VeSC applied to an N source and M load system is shown in figure 2.5.

Figure 2.5: Simplified circuit schematic of Vector Switching Converter (VeSC).

As may be seen from figure 2.5, one requires 3xNxM IGBTs to realize a vector switching converter that can interface N stiff three-phase voltage sources with M three-phase loads. The main motivation behind this converter is to regulate the fraction of the power drawn by each three-phase load from each of the three-phase AC sources. It may be observed that the function of each three-pole switch can be seen as selectively connecting the three phase pole current vector to the various three-phase throw voltage vectors, and varying the duty ratio of each throw to modulate the power transfer among them. These converters are termed as Vector Switching Converters, since the working principle of this converter is based on controlling the connectivity between various three-phase AC voltage or current vectors by switching among their components concurrently. It may be noted that a conventional matrix converter would require 9xNxM bidirectional switches or 18xNxM IGBTs for the same purpose [8]. However matrix converter allows significantly higher flexibility in the synthesis of output waveform in terms of its frequency and phase. While as vector switching converters are restricted to power conversion at fundamental frequency and can generate only synchronous voltages, matrix converters are capable of frequency conversion as well as synthesizing voltages that are asynchronous with the source voltage.

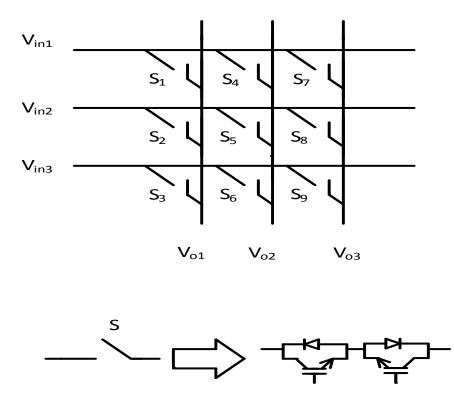

### 2.6. Matrix Converter

With the introduction of matrix converter, research on direct ac-ac power conversion without reactive components received a major boost. The matrix converter [9] has been introduced to obtain sinusoidal waveforms at both input and output ports. It has been used to incorporate bi-directionality in the converter circuit, implement independent control over input and output frequency as well as achieve variable output wave amplitude and phase. A conventional matrix converter interfacing a three phase voltage source to a three phase load is shown in figure 2.6. It may be observed that it requires 9 bidirectional or 9 IGBTs to realize the matrix converter. Thus, a matrix converter that interfaces N three phase voltage sources to M three phase loads requires 9xNxM bidirectional switches.

Figure 2.6: Simplified circuit schematic of a three phase to three phase matrix converter With nine bi-directional switches the matrix converter can theoretically assume 512 (29) different switching states combinations. But not all of them can be usefully employed. Regardless of the control method used, the choice of the matrix converter switching states combinations (also referred as matrix converter configurations) to be used must comply with two basic rules. As the converter is supplied by a voltage source and usually feeds an inductive load, the input phases should not be short-circuited and the output currents should not be interrupted. From a practical point of view these rules imply that one and

only one bi-directional switch per output phase must be switched on at any instant. Taking this constraint into account, there are 27 permitted switching combinations in a three phase to three phase matrix converter. The switching sequence of the matrix converter has been designed such that each output may be fed with a cyclic permutation of the input lines. This cyclic permutation also ensures that if the input three phase system is balanced, the three output phases are naturally equidisplaced.

## 2.7. Phase and Amplitude Controllable Transformer

The expansion of the applicability of ac choppers beyond voltage amplitude regulation to additional control of phase and frequency of output voltage has been accomplished by the introduction of the concept of dual virtual quadrature sources [10]. Previously, ac-ac direct power converters had been designed to be controlled by traditional duty cycle (varying between 0 and 1). Thus output voltage ( $V_0$ ) was governed by a simple scalar product of duty ratio (D) and input ac voltage ( $V_i \cos \theta$ ) as shown in equation (1).

$$V_{o} = D V_{i} \cos\theta \tag{1}$$

By introducing even harmonic terms in the duty ratio, output voltage can contain an additional quadrature component along with odd harmonics as shown in equations (2) and (3).

If

$$D = D_0 + D_2 \sin 2\theta + D_4 \sin 4\theta + D_6 \sin 6\theta + \dots$$

(2)

then,

$$Vo = D_{ref}V_i \cos(\theta + \alpha) + D_3V_i \sin 3\theta + D_5V_i \sin 5\theta + \dots$$

(3)

The third harmonic components get trapped in a three-wire system, and thus one can now regulate the phase and frequency content of output voltage to obtain desired fundamental and harmonic reference by controlling the amount of even harmonics introduced in the

Figure 2.7: Simplified circuit schematic of a Phase Amplitude Controllable Transformer A circuit schematic of PACT has been shown in figure 2.7. The PACT utilizes the principle of creating dual virtual quadrature sources that facilitates the generation of output voltages with controllable phase and/or harmonic levels without requiring the use of stored energy or additional sources and switches.

## 2.8. Multilevel Direct AC Converter

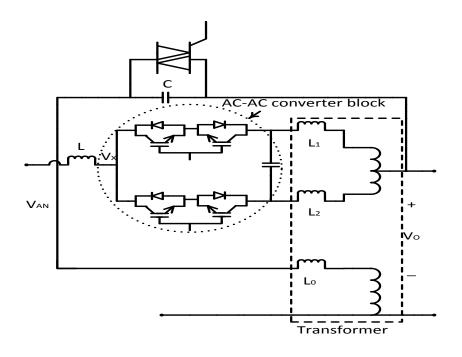

The concept of dual quadrature sources based duty ratio control has been extended to build Thin AC Converters (TACC) [2]. This TACC has been used to achieve dynamic control of the grid. Main control objective of TACC is different than inverter or matrix converter, which controlled the output voltage. TACC may be used to reflect modified asset characteristics on the line side, while using the asset within its design specifications. While the possibility of realizing AC-AC direct power conversion with single devices has been documented extensively in literature, employing this technology to utility scale voltages remains challenging. This is because of the fact that devices such as IGBTs have been predominantly limited to 1700V/1200A for fast switching applications at low cost. Larger devices have now been starting to become commonly available up to 3.3kV, but with slower switching speeds and at higher costs. On the other hand, 6.6kV IGBTs have been more recently introduced and have not been widely available in commercial markets. The ability to series connect these devices reliably has been studied, however it results in further lowering of switching speeds. Although several multilevel dc/ac converter topologies are well known, extending them to direct ac-ac conversion [23]-[27] has not been widely explored. Recently, a topology shown in figure 2.8 has been presented as multilevel ac-ac converter in [11]. Using this multilevel ac-ac converter, TACC can be implemented for higher grid voltages.

Figure 2.8: Simplified circuit schematic of multilevel ac-ac converter.

As may be seen from figure 2.8, a three-level ac-ac converter is constructed by cascading two ac-ac converters. Topologically similar to the flying capacitor multilevel

dc-ac inverter [12], [24], the goal is to clamp the voltage across each bidirectional switch by an intermediate capacitor. However, one of the challenges associated with this topology is voltage balancing and firm control of this floating capacitor. Hence, a voltage balancing transformer is proposed to mitigate this issue as shown in figure 2.8.

It may be observed from figure 2.8 that the multilevel ac-ac converter topology allows the employment of lower voltage rated IGBTs for building the bidirectional switches, thereby also reducing the switching losses to improve the converter efficiency. But the disadvantage of this converter topology lies in the fact that the number of passive components has increased with the introduction of the voltage balancing transformer. This also has led to significant increase in the size of the converter. Hence one could conclude that the direct ac-ac converters at higher voltages are a challenge to implement, due to lack of higher voltage rated semiconductor devices.

## CHAPTER 3 : CENTER-POINT-CLAMPED AC-AC BUCK CONVERTER

## 3.1. Introduction

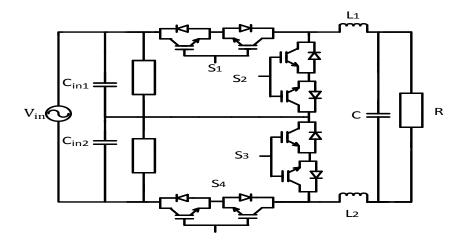

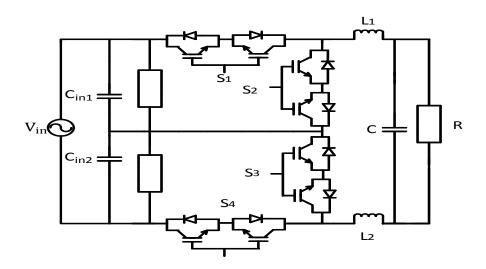

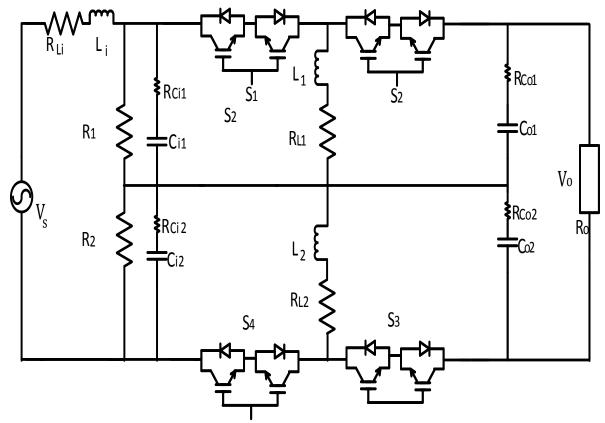

This chapter discusses a novel topology for ac-ac direct power conversion that is capable of providing access to the mid-voltage point on the source side. This arrangement offers a means to clamp the voltage across bidirectional switches at half the magnitude of source voltage, thereby allowing employment of low voltage power electronic devices to operate with higher system voltages. Unlike flying capacitor arrangement shown in figure 2.6, the proposed structure requires no transformer for capacitor balancing and follows principle of neutral-point-clamped dc-ac inverter introduced in [13].

Although it is tempting to term the proposed power circuit as an ac-ac 'multilevel' converter, careful examination reveals that contrary to multilevel dc-ac inverter, there are no multiple ac levels which add up to synthesize the output ac voltage. Instead, this converter functions to switch either between full input voltage wave ( $v_{in}\cos\theta$ ) and half input voltage wave ( $v_{in}/2\cos\theta$ ), or between half input voltage wave ( $v_{in}/2\cos\theta$ ) and zero(0) to realize the desired output ac voltage waveform. Hence this converter topology is termed as Center-Point-Clamped AC-AC Converter, and not multilevel ac-ac converter.

3.2. Evolution of Center-Point-Clamped AC-AC Converter

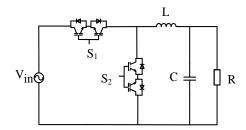

Figure 3.1: Simplified circuit schematics showing single phase ac-ac converter with two bidirectional switches.

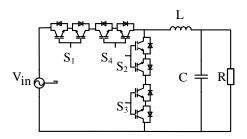

Figure 3.2: Simplified circuit schematics showing single phase ac-ac converter with four bidirectional switches.

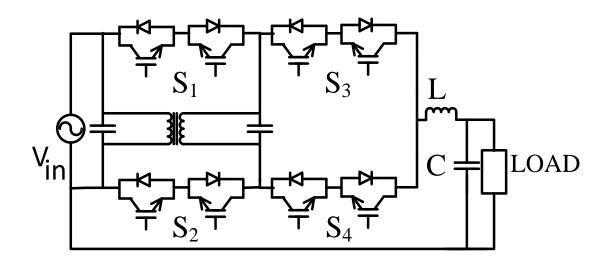

This section discusses the evolution of the Center-Point-Clamped AC-AC Converter. Simplified circuit schematic of an ac-ac converter topology with two bidirectional switches,  $S_1$  and  $S_2$  is shown in figure 3.1. The bidirectional switch has been realized by series connection of two back to back insulated gate bipolar transistors (IGBT) with anti-parallel diodes. The bi-directional switches,  $S_1$  and  $S_2$  are operated in a complementary fashion. When switch  $S_1$  is closed, switch  $S_2$  is open, and vice versa. A low pass L-C filter is to filter out the high frequency switching content to get back low frequency ac sinusoid at the output. It may be observed that when switch  $S_1$  is closed, entire input voltage  $v_{in}$  is impressed across switch  $S_2$ . Similarly, when switch  $S_2$  is closed, voltage across switch  $S_1$  is  $v_{in}$ . Thus, maximum voltage stress on switches  $S_1$  and  $S_2$  is the peak of input voltage,  $v_{in}$ . In order to employ power devices with limited blocking voltage capability in a system that exceeds these voltage ratings, one has to resort to series connection of switches.

In this chapter, the design of an ac-ac converter for 4.16kV three-phase distribution system has been discussed. The phase-neutral voltage for a single phase system translates to 2400V ac rms (or 3400V phase-neutral peak voltage) ( $v_{in}$ ). To ensure that the devices work reliably within their Safe Operating Area (SOA), it is required to employ either a 6.6kV IGBT or a series connection of two 3.3kV devices for this application. As 6.6kV devices are not widely available, our only alternative has been to employ series connection of two 3.3kV IGBTs. This is shown in figure 3.2, where each bidirectional switch is composed of four 3.3kV IGBTs.

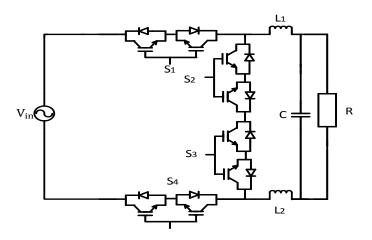

An ac-ac converter topology equivalent to the one in figure 3-1(b) is shown in figure 3.3. As may be seen from the simplified schematic of the single phase ac-ac converter in figure 3.3, the four bidirectional switches has been rearranged.

Figure 3.3 Simplified circuit schematic of single phase ac-ac converter.

As is well-known, it is challenging to ensure that the voltages across two series connected devices are distributed evenly during steady state and dynamic conditions. Solving this problem is one of the motivations for this thesis, and the first step towards realizing the Center-Point-Clamped AC-AC Converter topology is rearrangement of four bidirectional devices as shown in figure 3.3 to form a symmetrical converter topology. As may be seen from figure 3.3, the bidirectional switches S<sub>1</sub> and S<sub>4</sub>, S<sub>2</sub> and S<sub>3</sub> are series connected to withstand higher voltage ratings at the input. The switches, S<sub>1</sub>, S<sub>4</sub>, and S<sub>2</sub>, S<sub>3</sub> are operated in a complementary manner. When switches S<sub>1</sub> and S<sub>4</sub> are closed, entire input voltage is connected to the load. Whereas when switches S<sub>2</sub> and S<sub>3</sub> are closed, the source is disconnected and load current freewheels. In figure 3.3, inductor ( $L_1$ ), inductor ( $L_2$ ) and capacitor (C) are filter components. Load is represented by resistor (R).

3.3. Operating Principle of Center-Point-Clamped AC-AC Buck Converter

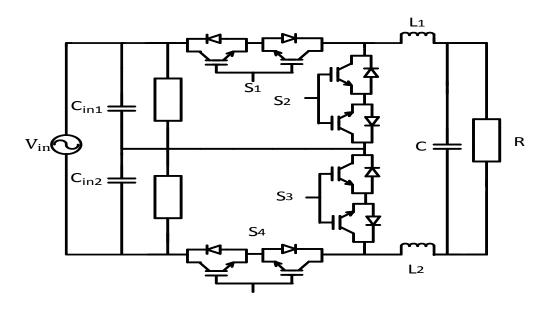

In order to achieve even distribution of voltage stresses on the four bidirectional switches under all operating conditions, a center point is constructed on the source side with two capacitors and is tied to the mid-point between switches  $S_2$  and  $S_3$ . This center-point provides an access to the midpoint of the input source voltage. Complete circuit of the proposed center point clamped ac-ac converter is shown in figure 3.4. The operating principle of this center-point-clamped ac-ac converter [37] can be thought of as similar to neutral-point-clamped dc-ac inverter [13] in the sense that output can be clamped to the center point of the input.

Figure 3.4 Simplified circuit schematic of single phase center point clamped ac-ac converter.

However, instead of generating three 'dc' levels at the pole output ( $-V_{dc}/2$ , 0,  $+V_{dc}/2$ ) as obtained in a conventional neutral-point-clamped inverter, realizing three distinct 'differential ac' outputs is the key point that distinguishes this topology. It may be observed that when switches S<sub>1</sub>, S<sub>4</sub> are closed and switches S<sub>2</sub>, S<sub>3</sub> are open, resultant output voltage is equal to input voltage  $v_{in}$ . However, because the mid-point between switches S<sub>2</sub> and S<sub>3</sub> is tied to center point on the source, the distribution of voltage between these two open switches S<sub>2</sub> and S<sub>3</sub> is identical and is equal to  $v_{in}/2$ . Similarly, when switches S<sub>2</sub>, S<sub>3</sub> are closed and switches S<sub>1</sub>, S<sub>4</sub> are open, the resultant output voltage is zero (0). Again, the distribution of voltage between two open switches S<sub>1</sub> and S<sub>4</sub> is identical and is equal to  $v_{in}/2$  because of clamp to the center point. Finally, when switches S<sub>1</sub> and S<sub>3</sub> are closed, the resultant output voltage is half the input voltage i.e.  $v_{in}/2$ . It may be noted that another combination with switches S<sub>2</sub> and S<sub>4</sub> closed gives the same result of voltage  $v_{in}/2$  across the load. However, the difference between these two operating conditions is the capacitor that gets connected to the load. Similar to the

classical neutral-point-clamped dc-ac inverter, these two states are alternately employed so as to evenly balance the voltages across the two capacitors. Switching pattern to generate an ac waveform of desired magnitude at the load side is presented in Table 1.

| Command    |                                      |                                      |

|------------|--------------------------------------|--------------------------------------|

| $v_{oref}$ | between 0 and                        | between $v_{in}/2$                   |

| (desired   | $v_{in}/2$                           | and $v_{in}$                         |

| output)    |                                      |                                      |

| State 1    | $S_2 S_3$ closed                     | S <sub>1</sub> S <sub>4</sub> closed |

|            | $S_1 S_4$ open                       | $S_2 S_3$ open                       |

| State 2    | S <sub>2</sub> S <sub>4</sub> closed | S <sub>2</sub> S <sub>4</sub> closed |

|            | $S_1 S_3$ open                       | $S_1 S_3$ open                       |

| State 3    | $S_2 S_3$ closed                     | S <sub>1</sub> S <sub>4</sub> closed |

|            | $S_1 S_4$ open                       | $S_2 S_3$ open                       |

| State 4    | $S_1 S_3$ closed                     | $S_1 S_3$ closed                     |

|            | $S_2 S_4$ open                       | $S_2 S_4$ open                       |

Table 1. Switching pattern of the proposed center-point-clamped ac-ac converter

One of the unique features of the proposed converter topology is the method to balance input side capacitor voltage for achieving consistent center-point voltage,  $v_{in}/2$ . As may be seen from Table 1, when switches S<sub>2</sub> and S<sub>3</sub> are closed for zero output voltage level in State 1, capacitors C<sub>i1</sub> and C<sub>i2</sub> get equally charged. In order to achieve output voltage  $v_{in}/2$ in State 2, switches S<sub>2</sub> and S<sub>4</sub> are closed. This results in discharging of C<sub>i1</sub> and charging of C<sub>i2</sub>. For the next zero output voltage level in State 3, switches S<sub>2</sub> and S<sub>3</sub> are closed as in State 1. However, for State 4, instead of S<sub>2</sub> and S<sub>4</sub> for  $v_{in}/2$ , we close S<sub>1</sub> and S<sub>3</sub>. Thus, in this state C<sub>i2</sub> gets discharged whereas C<sub>i1</sub> gets charged. This alternate charging and discharging sequence of capacitors C<sub>i1</sub> and C<sub>i2</sub> ensures input capacitor voltage balancing. This methodology of capacitor voltage balancing is also applied when the output voltage  $v_{oref}$  is regulated from  $v_{in}/2$  to  $v_{in}$ , as may be seen from Table 1.

<sup>3.4.</sup> Methodology for Balancing Voltages across Input capacitors

## CHAPTER 4 : CIRCUIT DESIGN OF CENTER-POINT-CLAMPED AC-AC BUCK CONVERTER

### 4.1. Introduction

This chapter discusses the design considerations for power circuit design of a center point clamped ac-ac converter. Power circuit design involves determination of the inductance and capacitance values in the converter system. These reactive elements may be represented as functions of inductor ripple current, capacitor ripple voltage and switching frequency. Values of reactive elements are determined using inductor volt-sec balance and capacitor current charge balance methods. Analysis and design methods applied to ac-ac converter are found to be similar to the corresponding dc-dc converter due to their design and functional similarities.

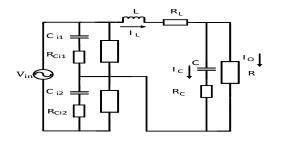

#### 4.2. Circuit Description

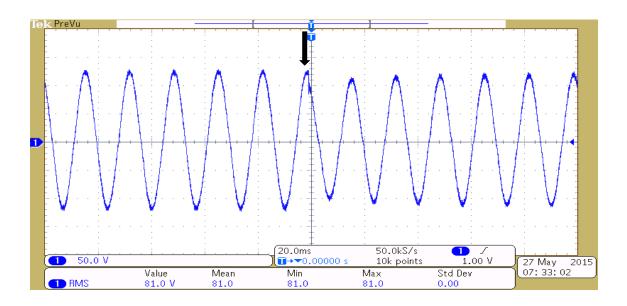

Figure 4.1: Simplified circuit schematic of a single phase of center-point-clamped ac-ac buck converter.

A simplified circuit schematic of a single phase of center-point-clamped ac-ac buck converter is shown in figure 4.1. A representative center-point-clamped ac-ac buck converter is designed for 4.16kV/1MW three-phase application. For a single phase system as shown in figure 4.1, this translates to 2400V ac rms phase-neutral input voltage (or 3400V phase-neutral peak voltage) ( $v_{in}$ ). The output voltage ( $v_o$ ) is desired to be set within 10% to 90% of  $v_{in}$ . This converter uses 4 bidirectional switches S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, and S<sub>4</sub> which are realized with 8 Insulated Gate Bipolar Transistors (IGBTs) that are switched at 1200Hz ( $f_{sw}$ ). Filter components include input capacitors  $C_{i1}$  and  $C_{i2}$ , output inductor (L) and output capacitor (C).  $R_{Ci1}$ ,  $R_{Ci2}$ ,  $R_L$  and  $R_C$  are parasitic resistances associated with these filter components and the load is represented by a resistor R. We neglect the dynamics associated with input filter capacitors  $C_{i1}$ ,  $C_{i2}$ , and their parasitic resistances  $R_{Ci1}$  and  $R_{Ci2}$ . Hence it is assumed that input voltage is split evenly between the two filter capacitors at any given time.

When switches  $S_1$  and  $S_4$  are closed, and switches  $S_2$  and  $S_3$  are open, output voltage is  $v_{in}$ . When switches  $S_1$  and  $S_4$  are open, and switches  $S_2$  and  $S_3$  are closed, output voltage is 0. And lastly, when switches  $S_1$  and  $S_3$  (or  $S_2$  and  $S_4$ ) are closed and switches  $S_2$  and  $S_4$  (or  $S_1$  and  $S_3$ ) are open, output voltage is  $v_{in}/2$ . Thus when the desired output voltage is less than 50% of  $v_{in}$ , then the converter is switched between 0 and  $v_{in}/2$ . Whereas, when the desired output voltage is more than 50% of  $v_{in}$ , then the converter is switched between  $v_{in}/2$  and  $v_{in}$ .

#### 4.3. Power Circuit Design

Let us consider 2 regions, in region1 desired output voltage ranges from 0 to  $v_{in}/2$ , and in region 2 desired output voltage ranges from  $v_{in}/2$  to  $v_{in}$ . Region 1: (desired  $v_o$  ranges from 0 to  $v_{in}/2$ ):

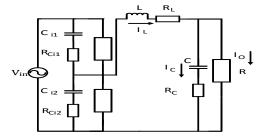

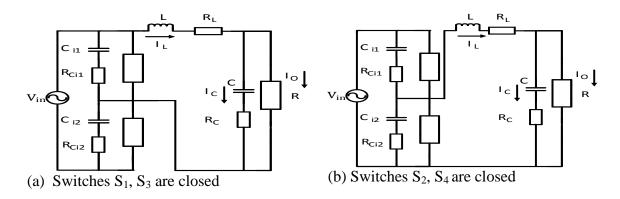

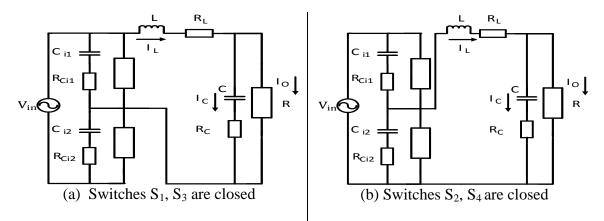

Interval  $T_1$  (switches  $S_1$ ,  $S_3$  (or  $S_2$ ,  $S_4$ ) are closed and  $S_2$ ,  $S_4$  (or  $S_1$ ,  $S_3$ ) are open) as shown in figure 4.2.

(a) Switches  $S_1$ ,  $S_3$  are closed and  $S_2$ ,  $S_4$  (b) Switches  $S_2$ ,  $S_4$  are closed and  $S_1$ ,  $S_3$  are open. are open.

Figure 4.2: Equivalent circuit of center-point-clamped ac-ac converter in interval T<sub>1</sub>.

Applying Kirchoff's voltage laws, we get

$$\frac{v_{in}}{2} - v_L - i_L R_L - v_o = 0 \tag{4.1}$$

Therefore,

$$v_L = \frac{v_{in}}{2} - i_L R_L - v_o \tag{4.2}$$

Current through capacitor,

$$i_c = i_L - \frac{v_o}{R} \tag{4.3}$$

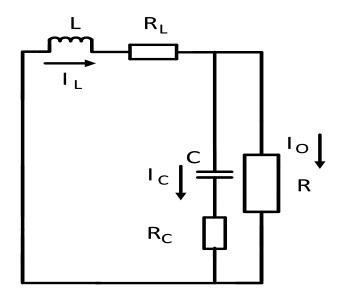

In interval  $T_2$  switches  $S_2$ ,  $S_3$  are closed and switches  $S_1$ ,  $S_4$  are open. The equivalent circuit of center point clamped ac-ac converter in interval  $T_2$  is shown in figure 4.3.

Figure 4.3: Equivalent circuit of center-point-clamped ac-ac converter in interval T<sub>2</sub>. Applying Kirchoff's voltage laws, we get

$$v_L + i_L R_L + v_o = 0 (4.4)$$

Therefore,

$$v_L = -i_L R_L - v_o \tag{4.5}$$

Current through capacitor,

$$i_c = i_L - \frac{v_o}{R} \tag{4.6}$$

Let the time period be *T* and *d* be the duty ratio. Thus, *dT* is the time when switches  $S_2$ ,  $S_4$  are closed and also when switches  $S_1$ ,  $S_3$  are closed. For interval  $T_1$ , let the duration of operation be 2*dT*. In interval  $T_2$ , duration of operation will be,

$$T - 2dT = (1 - 2d)T (4.7)$$

$$T = \frac{1}{f_{sw}} \tag{4.8}$$

$f_{sw}$  is the switching frequency.

In steady-state operation, average inductor voltage and average capacitor current over time period T must be zero.

Average inductor voltage,

$$\langle v_L \rangle = (\frac{v_{in}}{2} - i_L R_L - v_o) 2d + (-i_L R_L - v_o)(1 - 2d)$$

(4.9)

$$(2d)\frac{v_{in}}{2} - v_o - i_L R_L = 0 \tag{4.10}$$

Average capacitor current,

$$\langle i_c \rangle = (i_L - \frac{v_o}{R})2d + (i_L - \frac{v_o}{R})(1 - 2d)$$

(4.11)

$$i_L - \frac{v_o}{R} = 0$$

(4.12)

Substituting equation (4.12) in (4.10)

$$(2d)\frac{v_{in}}{2} - v_o - \left(\frac{v_o}{R}\right)R_L = 0 \tag{4.13}$$

$$(2d)\frac{v_{in}}{2} - v_o \left(1 + \left(\frac{R_L}{R}\right)\right) = 0 \tag{4.14}$$

We get,

$$\frac{v_o}{v_{in}} = \frac{d}{\left(\frac{R_L}{R} + 1\right)} \tag{4.15}$$

Since  $R_L \ll R$ ,

$$v_0 = d v_{in} \tag{4.16}$$

In interval  $T_1$ , from equation (4.1),

$R_L \ll R$ , we can neglect the voltage drop across the parasitic resistance of inductor.

So,

$$v_L = (\frac{v_{in}}{2} - v_o)$$

(4.17)

31

$$L\frac{di_L}{dt} = \left(\frac{v_{in}}{2} - v_o\right) \tag{4.18}$$

$$\Delta i_L = \frac{(\frac{v_{in}}{2} - v_o)}{L} (2d)T$$

(4.19)

peak to peak  $\Delta i_L = \frac{\left(\frac{v_{in}}{2} - v_o\right)}{L} (2d)T$  (4.20)

$\Delta i_L$  is taken as 10% of inductor current  $i_L$ , we can get  $i_L$ , from equation (4.12)

Therefore,

$$L = \frac{\left(\frac{\nu_{in}}{2} - \nu_o\right)}{\Delta i_L} (2d)T$$

(4.21)

total charge deposited on capacitor plates Q is given by,

$$Q = \Delta v_C C \tag{4.22}$$

Since  $R_C$  is negligible,  $v_C$  is equal to  $v_o$ .  $\Delta v_c$  is taken as 10% of capacitor voltage  $v_o$ .

Total charge Q is the area of triangle of  $\Delta i_L$  waveform [13],

$$Q = \frac{1}{2} \frac{\Delta i_L}{2} \frac{T}{2}$$

$$\tag{4.23}$$

Substituting equation (4.23) in (4.22)

$$C = \frac{\Delta i_L T}{8\Delta v_C} \tag{4.24}$$

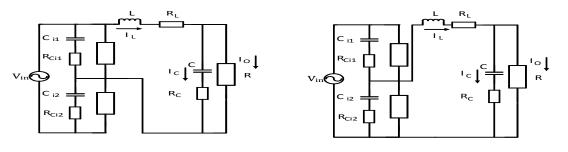

Region 2: (desired  $v_o$  ranges from  $v_{in}/2$  to  $v_{in}$ ):

Interval  $T_1$  (switches  $S_1$ ,  $S_3$  (or  $S_2$ ,  $S_4$ ) are closed and  $S_2$ ,  $S_4$  (or  $S_1$ ,  $S_3$ ) are open) as shown in figure 4.4.

Figure 4.4: Equivalent circuit of center-point-clamped ac-ac converter in interval T<sub>1</sub>.

Applying Kirchoff's voltage laws, we get

$$\frac{v_{in}}{2} - v_L - i_L R_L - v_o = 0 \tag{4.25}$$

Therefore,

$$v_L = \frac{v_{in}}{2} - i_L R_L - v_o \tag{4.26}$$

Current through capacitor,

$$i_c = i_L - \frac{v_o}{R} \tag{4.27}$$

In interval  $T_2$ , switches  $S_2$ ,  $S_4$  are closed and switches  $S_1$ ,  $S_3$  are open. The equivalent circuit of ac-ac converter in interval  $T_2$  is shown in figure 4.5.

Figure 4.5: Equivalent circuit of center-point-clamped ac-ac converter in interval T<sub>2</sub>.

Applying Kirchoff's voltage laws, we get

$$v_{in} - v_L - i_L - v_o = 0 \tag{4.28}$$

Therefore,

$$v_L = v_{in} - i_L R_L - v_o \tag{4.29}$$

Current through capacitor,

$$i_c = i_L - \frac{v_o}{R} \tag{4.30}$$

Let the time period be *T*. *dT* is the time period when switches  $S_2$ ,  $S_4$  are closed and switches  $S_1$ ,  $S_3$  are open. In interval  $T_1$ , switches  $S_1$ ,  $S_3$  (or  $S_2$ ,  $S_4$ ) are closed and  $S_2$ ,  $S_4$  (or  $S_1$ ,  $S_3$ ) are open,

$$T - dT = (1 - d)T (4.31)$$

$$T = \frac{1}{f_{sw}} \tag{4.32}$$

34

In steady-state operation, average inductor voltage and average capacitor current over time period T must be zero.

Average inductor voltage

$$\langle v_L \rangle = \left(\frac{v_{in}}{2} - i_L R_L - v_o\right)(1 - d) + (v_{in} - i_L R_L - v_o) d$$

(4.33)

$$(1+d)\frac{v_{in}}{2} - v_o - i_L R_L = 0 \tag{4.34}$$

Average capacitor current,

$$\langle i_c \rangle = (i_L - \frac{v_o}{R})D + (i_L - \frac{v_o}{R})(1 - D)$$

(4.35)

$$i_L - \frac{v_o}{R} = 0$$

(4.36)

Substituting equation (4.36) in (4.34)

$$(1+d)\frac{v_{in}}{2} - v_o - (\frac{v_o}{R})R_L = 0$$

(4.37)

$$(1+d)\frac{v_{in}}{2} - v_o(1+\left(\frac{R_L}{R}\right)) = 0$$

(4.38)

$$\frac{V_o}{V_{in}} = \frac{d+1}{2(\frac{R_L}{R}+1)}$$

(4.39)

In interval  $T_2$ , from equation (4.29),

Since  $R_L \ll R$ , we can neglect the voltage drop across the parasitic resistance of inductor.

So,

$$v_L = v_{in} - v_o$$

(4.40)

$$L\frac{dI_L}{dt} = v_{in} - v_o \tag{4.41}$$

35

$$\Delta i_L = \frac{v_{in} - v_o}{L} dT \tag{4.42}$$

peak to peak  $\Delta i_L = \frac{v_{in} - v_o}{L} dT$  (4.43)

$\Delta i_L$  is taken as 10% of inductor current  $i_{L_{i,j}}$  we can get  $i_L$ , from equation (4.36)

Therefore,

$$L = \frac{v_{in} - v_o}{\Delta i_L} dT \tag{4.44}$$

Total charge deposited on capacitor plates Q is given by,

$$Q = C\Delta v_C \tag{4.45}$$

Since  $R_C$  is negligible,  $v_C$  is equal to  $v_o$ .  $\Delta v_C$  is taken as 10% of capacitor voltage  $v_o$ .

Total charge Q is the area of triangle of  $\Delta i_L$  waveform [13]

$$Q = \frac{1}{2} \frac{\Delta i_L}{2} \frac{T}{2}$$

$$\tag{4.46}$$

Substituting equation (4.46) in (4.45)

$$C = \frac{\Delta i_L T}{8\Delta v_C} \tag{4.47}$$

Substituting values of  $v_o$ ,  $v_{in}$ , d, T,  $\Delta i_L$ ,  $\Delta v_C$  in equations (4.21), (4.24) (4.44), (4.47), we can get inductance and capacitance values as shown in Table 2.

Table 4.1 Inductance and capacitance values of CENTER-POINT-CLAMPED ac-ac converter.

|          | Desired $v_o$       | D   | L       | С       |

|----------|---------------------|-----|---------|---------|

| Region1  | $0.1 v_{\rm in}$    | 0.1 | 2.3 mH  | 300 µF  |

|          | $0.4 v_{in}$        | 0.4 | 9.25 mH | 18.8 µF |

| Region 2 | $0.6 v_{in}$        | 0.2 | 13.8 mH | 8.34 μF |

|          | 0.9 v <sub>in</sub> | 0.8 | 20.8 mH | 3.71 μF |

For L > 20.8 mH, the converter enters the discontinuous conduction mode and for L < 20.8 mH, the converter cannot operate in region 2, for  $v_{ref} = 0.9 v_{in}$ . For  $C < 300 \mu$ F, the converter cannot operate in region 1,  $v_{ref} = 0.1 v_{in}$ . So we select output filter components values in such a way that the converter can operate in both regions 1 and 2.

Therefore, output filter components values are,

$$L = 20.8 \text{ mH}$$

$$C = 300 \text{ }\mu\text{F}$$

## CHAPTER 5 : DYNAMIC ANALYSIS OF CENTER-POINT-CLAMPED AC-AC BUCK CONVERTER

### 5.1. Introduction

In this chapter using a state space modelling and an average technique, transfer functions  $G_d$  (transfer function between the output voltage to duty ratio) and  $G_v$  (transfer function between the output voltage to input voltage) for the center point clamped ac-ac converter are derived. Frequency response of the system is evaluated using transfer functions  $G_v$  and  $G_d$ .

### 5.2. Circuit Description

A simplified circuit schematic of a single phase of center-point-clamped ac-ac converter is shown in Figure 5.1.

- Figure 5.1: Simplified circuit schematic of a single phase of center-point-clamped ac-ac buck converter.

- A representative center-point-clamped ac-ac buck converter circuit description is

same as given in chapter 4.

# 5.3. State Space Equations

State space equations for a generic switched circuit that is operated in two intervals  $T_1$  and  $T_2$  are given by:

I. Interval T<sub>1</sub> (operating for duration

$$dT$$

in a given time period T)

$\dot{x} = A_1 x + b_1 u$  (5.1)

Interval T<sub>2</sub> (operating for duration (1-d)T in a given time period *T*) II.

$$\dot{x} = A_2 x + b_2 u \tag{5.3}$$

$$y = c_2^T x (5.4)$$

where *x* is the state of the system, *u* is the input, and *y* is the output [14]

State space equations in interval  $T_1$  can be expressed with reference to *d* as:

$$\dot{x} = (A_1 x + b_1 u) d \tag{5.5}$$

State space equations in interval  $T_2$  can be expressed with reference to (1-d) as:

$$\dot{x} = (A_2 x + b_2 u)(1 - d) \tag{5.7}$$

$$y = c_2^T x (1 - d) (5.8)$$

Averaging both sets of equations for the two switched intervals we get

$$\dot{x} = d(A_1 x + b_1 u) + (1 - d)(A_2 x + b_2 u)$$

(5.9)

$$y = dc_1^T x + (1 - d)c_2^T x (5.10)$$

.\_ \_

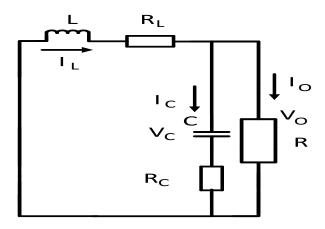

### 5.4. Dynamic Analysis

For the center-point-clamped ac-ac buck converter circuit shown in Figure 5.1, state variables are inductor current,  $i_L$ , and capacitor voltage,  $v_c$ . Input is input voltage  $v_{in}$ , and output is output voltage  $v_o$

Let us consider 2 regions, in region 1 desired output voltage ranges from 0 to  $v_{in}/2$ , and in region 2 desired output voltage ranges from  $v_{in}/2$  to  $v_{in}$ .

Region 1: (desired  $v_o$  ranges from 0 to  $v_{in}/2$ ):

Interval  $T_1$  (switches  $S_1, S_3$  (or  $S_2, S_4$ ) are closed and  $S_2, S_4$  (or  $S_1, S_3$ ) are open) as shown in Figure 5.2.

(a) Switches  $S_1$ ,  $S_3$  are closed and  $S_2$ ,  $S_4$  (b) Switches  $S_2$ ,  $S_4$  are closed and  $S_1$ ,  $S_3$  are open. are open.

Figure 5.2: Equivalent circuits of a center-point-clamped ac-ac converter in interval T<sub>1</sub>.

Applying Kirchoff's voltage laws, we get

$$\frac{v_{in}}{2} = i_L R_L + L \frac{di_L}{dt} + R_c (i_L - i_o) + v_c$$

(5.11)

$$v_c = (i_o - i_L)R_c + i_o R (5.12)$$

Rearranging equation 5.12,

$$i_o = \frac{v_c + i_L R_c}{R_c + R} \tag{5.13}$$

Substituting  $i_o$  in equation 5.11,

$$\frac{v_{in}}{2} = i_L R_L + L \frac{di_L}{dt} + R_c \left( i_L - \frac{v_c + i_L R_c}{R_c + R} \right) + v_c$$

(5.14)

$$\frac{v_{in}}{2} = i_L R_L + L \frac{di_L}{dt} + R_c \left(\frac{-v_c + i_L R}{R_c + R}\right) + v_c$$

(5.15)

$$\frac{\nu_{in}}{2} = i_L R_L + L \frac{di_L}{dt} + R_c \left(\frac{i_L R}{R_c + R}\right) - R_c \left(\frac{\nu_c}{R_c + R}\right) + \nu_c$$

(5.16)

$$\frac{v_{in}}{2} = i_L (R_L + R || R_c) + L \frac{di_L}{dt} + R \left( \frac{v_c}{R_c + R} \right)$$

(5.17)

Thus, state equation for  $i_L$  is,

$$\frac{di_L}{dt} = -\frac{\left(R_L + (R||R_c)\right)}{L} i_L - \frac{R}{(R+R_c)L} v_c + \frac{1}{2L} v_{in}$$

(5.18)

Applying Kirchoff's current law, we get

$$(i_L - i_o) = C \frac{dv_c}{dt}$$

(5.19)

Substituting  $i_o$  in equation 5.19,

$$\left(i_L - \frac{v_c + i_L R_c}{R_c + R}\right) = C \frac{dv_c}{dt}$$

(5.20)

Thus, state equation for  $v_c$  is,

$$\frac{dv_c}{dt} = \frac{R}{(R+R_c)C} i_L - \frac{1}{(R+R_c)C} v_C$$

(5.21)

We can combine equations 5.18 and 5.21 to give

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_c}{dt} \end{bmatrix} = \begin{bmatrix} \frac{-(R_L + (R_c \mid \mid R))}{L} & -\frac{R}{(R + R_c)L} \\ \frac{R}{(R + R_c)C} & -\frac{1}{(R + R_c)C} \end{bmatrix} \begin{bmatrix} i_L \\ v_c \end{bmatrix} + \begin{bmatrix} \frac{1}{2L} \\ 0 \end{bmatrix} v_{in}$$

(5.22)

Finally, output equation for  $v_o$  is,

$$[v_o] = \begin{bmatrix} R_c \mid \mid R & \frac{R}{R+R_c} \end{bmatrix} \begin{bmatrix} i_L \\ v_c \end{bmatrix}$$

(5.23)

Interval  $T_2$  (switches  $S_1, S_4$  are open and switches  $S_2, S_3$  are closed) as shown in figure 5.3:

Figure 5.3: Equivalent circuit of a center-point-clamped ac-ac converter in interval  $T_2$ .

Applying Kirchoff's voltage laws, we get

$$0 = i_L R_L + L \frac{di_L}{dt} + R_c (i_L - i_o) + v_c$$

(5.24)

$$v_c = (i_o - i_L)R_c + i_o R \tag{5.25}$$

Rearranging equation 5.25,

$$i_o = \frac{v_c + i_L R_c}{R_c + R} \tag{5.26}$$

Substituting  $i_o$  in equation 5.24,

$$0 = i_L R_L + L \frac{di_L}{dt} + R_c \left( i_L - \frac{v_c + i_L R_c}{R_c + R} \right) + v_c$$

(5.27)