## BEST PRACTICES FOR BUILDING HARDWARE DESIGNS FOR LIVING COMPUTATIONAL SCIENCE APPLICATIONS

by

Robin Jacob Pottathuparambil

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2013

Approved by:

Dr. Ronald R. Sass

Dr. James M. Conrad

Dr. Bharat S. Joshi

Dr. Ryan Adams

Dr. Taghi Mostafavi

© 2013 Robin Jacob Pottathuparambil ALL RIGHTS RESERVED

#### ABSTRACT

## ROBIN JACOB POTTATHUPARAMBIL. Best practices for building hardware designs for living computational science applications. (Under the direction of DR. RONALD R. SASS)

Scientific computing or Computational science, is a field of study where engineers and scientists use computer simulations to solve equations that model the physical world. In some cases, these equations come from the first principles of physics. In the past, these simulations were run on a single processor machine. However, due to various technological reasons, the performance of these machines are not likely to improve at the same rate as in the past. In order to improve the performance per watt of these simulations, special-purpose hardware accelerators can be used. This work mainly focuses on using FPGA-based hardware accelerators. In order to run these simulations on an FPGA accelerator, the application code needs to be re-factored into software and hardware sections. These faster simulations have motivated scientists to capture more behavior of the physical world. As additional behavior is captured, the application code needs to be re-factored each time, and a significant effort is required to re-build the design. Unfortunately, these multiple cycles of re-design reduces the overall productivity of scientists and engineers.

This work proposes a set of hardware design guidelines for changing computational science codes or living computational science codes. These guidelines co-evolve the hardware with the software, reducing the overall effort of re-design and improving productivity. The design guidelines are evaluated for effectiveness, communicability, and broad applicability. Experimental results have shown that the overall re-design effort is reduced, and these guidelines are broadly applicable to a wide variety of scientific computing applications.

## ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my advisor, Dr. Ronald R. Sass, his patience, effort, constant encouragement, constructive feedback, and for his dedicated support for my doctoral study and research.

I am also grateful to my dissertation committee members, Dr. James M. Conrad, Dr. Bharat S. Joshi, Dr. Ryan Adams, and Dr. Taghi Mostafavi, for their feedback and comments.

I also thank all the Reconfigurable Computing Systems (RCS) lab members who have directly and indirectly helped me in my research. I also thank all my lab members for the research discussions we had during my doctoral study.

Finally, I would like to thank my parents, P.K. Jacob and Sophy Jacob, and my brother, Justin Jacob, who have patiently supported me spiritually and financially to complete my doctoral study.

# TABLE OF CONTENTS

| LIST OF TABLES viii                |        |                                             |      |

|------------------------------------|--------|---------------------------------------------|------|

| LIST OF FIGURES x                  |        |                                             |      |

| LIST O                             | F ABB  | REVIATIONS                                  | xiii |

| CHAPT                              | TER 1: | INTRODUCTION                                | 1    |

| 1.1                                | Comp   | uter Simulations                            | 1    |

| 1.2                                | Hardv  | vare Accelerators                           | 3    |

| 1.3                                | Cost o | of Refactoring                              | 5    |

| 1.4                                | Evalu  | ation                                       | 8    |

|                                    | 1.4.1  | Experiment 1: Effectiveness                 | 9    |

|                                    | 1.4.2  | Experiment 2: Broad Applicability           | 12   |

| CHAPT                              | TER 2: | BACKGROUND                                  | 14   |

| 2.1 Field-Programmable Gate Arrays |        | 14                                          |      |

|                                    | 2.1.1  | Configurable Logic Blocks                   | 14   |

|                                    | 2.1.2  | Digital Clock Managers                      | 15   |

|                                    | 2.1.3  | Block RAMs                                  | 16   |

|                                    | 2.1.4  | PPC 405 Processor                           | 16   |

|                                    | 2.1.5  | XtremeDSP Tile                              | 16   |

|                                    | 2.1.6  | Ethernet MAC Block                          | 17   |

| 2.2                                | Relate | ed                                          | 18   |

|                                    | 2.2.1  | Hardware/Software Co-Design                 | 18   |

|                                    | 2.2.2  | Scientific Application Design Methodologies | 18   |

|                                    | 2.2.3  | HDL Coding and Design Guidelines            | 19   |

|                                    | 2.2.4  | C-to-HDL Conversion Tools                   | 19   |

| CHAPT                              | TER 3: | SCOPE AND METHODOLOGY                       | 22   |

| 3.1 Key Idea                       |        | 22                                          |      |

|                      |         |                                                | vi |

|----------------------|---------|------------------------------------------------|----|

| 3.2                  | Scope   | of the Work                                    | 23 |

| 3.3                  | Analy   | sis of Sequential Code                         | 24 |

|                      | 3.3.1   | Example: Electrodynamics Application           | 26 |

| 3.4                  | Hardw   | vare Design                                    | 29 |

| CHAPT                | TER 4:  | EVALUATION AND VALIDATION                      | 32 |

| 4.1                  | Effecti | iveness of design guideline                    | 32 |

|                      | 4.1.1   | Design Guideline Evaluation Metrics            | 33 |

|                      | 4.1.2   | Applications and Kernel Under Test             | 37 |

| 4.2                  | Comm    | nunicability of the Design Guidelines          | 58 |

| 4.3                  | Broad   | Applicability of the Design Guidelines         | 58 |

|                      | 4.3.1   | Guideline Fitness Plot                         | 59 |

|                      | 4.3.2   | Computational Fluid Dynamics                   | 60 |

|                      | 4.3.3   | Computational Molecular Dynamics               | 61 |

|                      | 4.3.4   | Quantum Monte Carlo Simulations                | 63 |

|                      | 4.3.5   | Hessenberg Reduction                           | 63 |

|                      | 4.3.6   | Gaxpy - BLAS Routine                           | 65 |

|                      | 4.3.7   | N-Body Simulations                             | 66 |

| 4.4                  | Valida  | tion                                           | 67 |

| CHAPTER 5: RESULTS 7 |         | 72                                             |    |

| 5.1                  | Effecti | iveness of design guidelines                   | 72 |

|                      | 5.1.1   | P-V System Modeling using Neural Networks (NN) | 72 |

|                      | 5.1.2   | 2D-Finite Difference Time Domain               | 78 |

|                      | 5.1.3   | Sparse Matrix Vector Multiplication            | 88 |

| 5.2                  | Broad   | Applicability of the Design Guidelines         | 95 |

|                      | 5.2.1   | Computational Fluid Dynamics                   | 96 |

|                      | 5.2.2   | Computational Molecular Dynamics               | 97 |

|                      | 5.2.3   | Quantum Monte Carlo Simulations                | 98 |

|                       |                      | vii |

|-----------------------|----------------------|-----|

| 5.2.4                 | Hessenberg Reduction | 101 |

| 5.2.5                 | Gaxpy - BLAS Routine | 101 |

| 5.2.6                 | N-Body Simulations   | 103 |

| CHAPTER 6: CONCLUSION |                      | 107 |

| REFERENCES            |                      | 109 |

# LIST OF TABLES

| TABLE 3.1:    | Design guidelines for living computational science applications      | 30 |

|---------------|----------------------------------------------------------------------|----|

| TABLE 4.1:    | Design guidelines for living computational science applications      | 35 |

| TABLE 4.2:    | Version 1.0 P-V generation model HW design                           | 39 |

| TABLE 4.3:    | Version 2.0 P-V generation, regulation, and battery model design     | 41 |

| TABLE 4.4:    | Hardware design details for version 1.0 electromagnetic application  | 47 |

| TABLE $4.5$ : | Hardware design details for version 2.0 electromagnetic application  | 48 |

| TABLE 4.6:    | Hardware design details for version 3.0 electromagnetic application  | 51 |

| TABLE 4.7:    | Hardware design details for version $1.0 \text{ SpMV}$ multiply unit | 53 |

| TABLE 4.8:    | Hardware design details for version 2.0 SpMV multiply unit           | 55 |

| TABLE 4.9:    | Hardware design details for version $3.0 \text{ SpMV}$ multiply unit | 56 |

| TABLE 4.10:   | CFD design evaluated using the design guidelines                     | 62 |

| TABLE 5.1:    | HDL synthesis report for P-V regulator model                         | 74 |

| TABLE 5.2:    | Results for P-V Modeling Application                                 | 75 |

| TABLE 5.3:    | Comparison of version 1 and 2 results for FDTD application           | 82 |

| TABLE $5.4$ : | Comparison of version 2 and 3 results for FDTD application           | 85 |

| TABLE 5.5:    | Comparison of reported versus used resources for applications        | 85 |

| TABLE 5.6:    | Performance for SpMV version 1 LFHD design                           | 89 |

| TABLE 5.7:    | Performance for SpMV version 2 LFHD design                           | 90 |

| TABLE 5.8:    | Performance for SpMV version 3 LFHD design                           | 90 |

| TABLE 5.9:    | Performance for SpMV Version 1 GFHD design                           | 91 |

| TABLE 5.10:   | Performance for SpMV Version 1 GFHD design                           | 92 |

| TABLE 5.11:   | Performance for SpMV Version 1 GFHD design                           | 92 |

| TABLE 5.12:   | Comparison of version 1 and 2 results for SpMV application           | 92 |

| TABLE 5.13:   | Comparison of version 2 and 3 results for SpMV application           | 93 |

| TABLE 5.14:   | CFD design evaluated using the design guidelines                     | 97 |

|                                                                 | ix  |

|-----------------------------------------------------------------|-----|

| TABLE 5.15: MD design evaluated using the design guidelines     | 99  |

| TABLE 5.16: QMC design evaluated using the design guidelines    | 100 |

| TABLE 5.17: HR design evaluated using the design guidelines     | 102 |

| TABLE 5.18: Gaxpy design evaluated using the design guidelines  | 103 |

| TABLE 5.19: N-body design evaluated using the design guidelines | 105 |

# LIST OF FIGURES

| FIGURE 1.1:  | Sequential and parallel tasks                               | 2  |

|--------------|-------------------------------------------------------------|----|

| FIGURE 1.2:  | Computing using hardware accelerators                       | 5  |

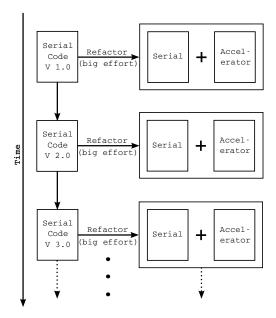

| FIGURE 1.3:  | Human effort over time due code evolution                   | 6  |

| FIGURE 1.4:  | Key idea                                                    | 7  |

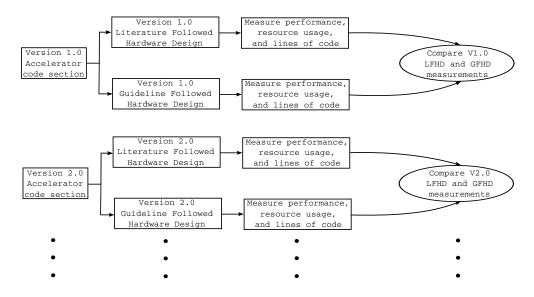

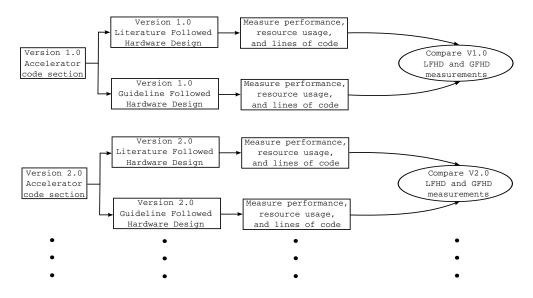

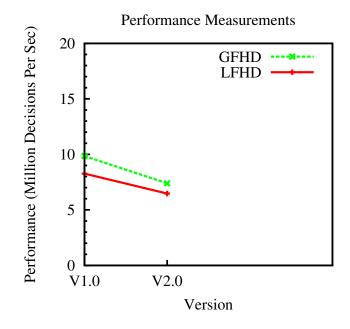

| FIGURE 1.5:  | LFHD and GFHD evaluation                                    | 12 |

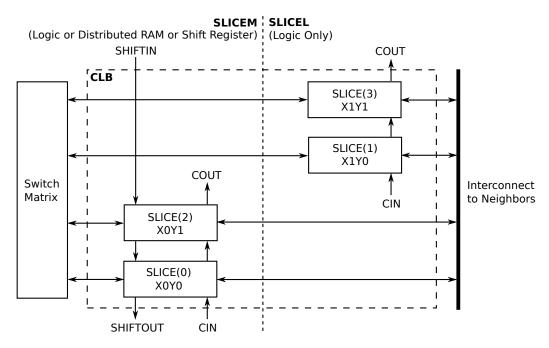

| FIGURE 2.1:  | Configurable logic blocks and slices of a Virtex 4 FPGA     | 15 |

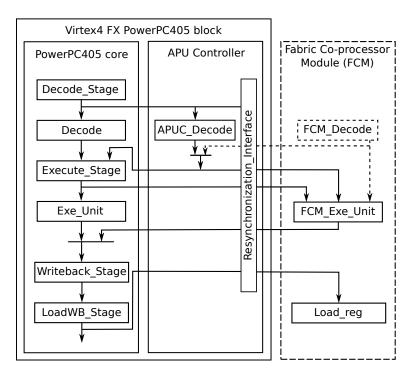

| FIGURE 2.2:  | PPC, APU, and FCM interaction                               | 17 |

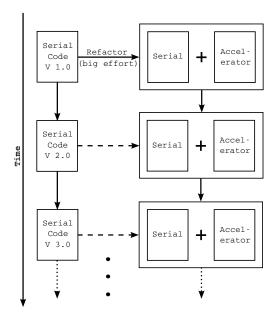

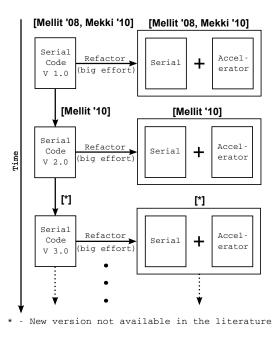

| FIGURE 3.1:  | Effort due code evolution                                   | 23 |

| FIGURE 3.2:  | Key idea                                                    | 24 |

| FIGURE 3.3:  | Analysis and pre-design                                     | 27 |

| FIGURE 3.4:  | FDTD Profile Information                                    | 28 |

| FIGURE 3.5:  | Hardware design                                             | 31 |

| FIGURE 4.1:  | LFHD and GFHD evaluation                                    | 36 |

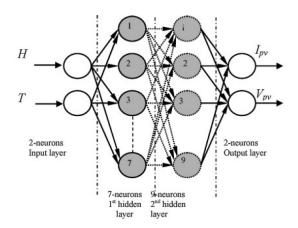

| FIGURE 4.2:  | Versions of P-V system modeling using NN                    | 39 |

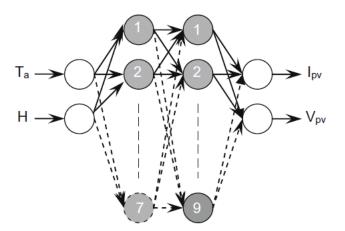

| FIGURE 4.3:  | Version 1.0: P-V generation NN model [1]                    | 40 |

| FIGURE 4.4:  | Version 1.0: P-V generation hardware design [1]             | 40 |

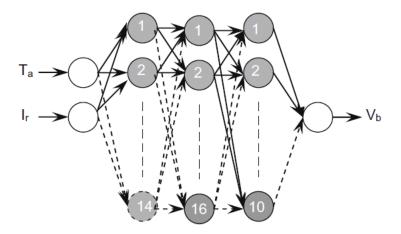

| FIGURE 4.5:  | Version 2.0: P-V generator NN model [2]                     | 41 |

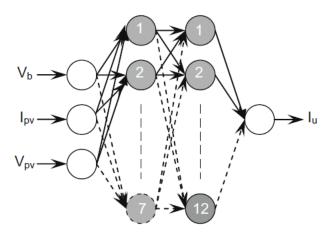

| FIGURE 4.6:  | Version 2.0: P-V battery charging NN model [2]              | 42 |

| FIGURE 4.7:  | Version 2.0: P-V regulator NN model [2]                     | 42 |

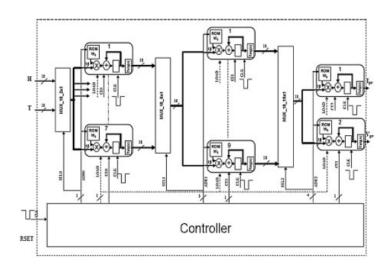

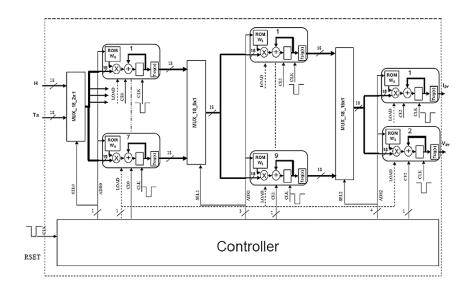

| FIGURE 4.8:  | Version 2.0: P-V generator hardware design [2]              | 43 |

| FIGURE 4.9:  | Version 2.0: P-V battery charging hardware design [2]       | 43 |

| FIGURE 4.10: | Version 2.0: P-V regulator hardware design [2]              | 44 |

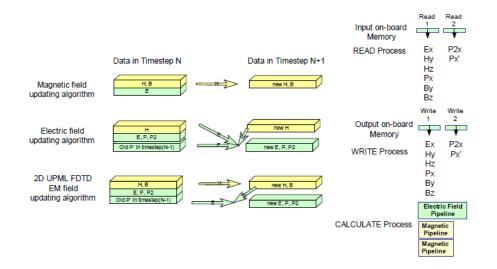

| FIGURE 4.11: | 2D-FDTD hardware design versions                            | 46 |

| FIGURE 4.12: | Version 1.0: 2D-FDTD hardware design [3]                    | 47 |

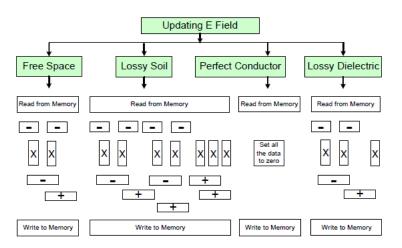

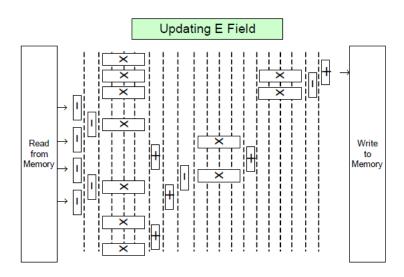

| FIGURE 4.13: | Version 2.0: 2D-FDTD 'E' field updating hardware design [4] | 48 |

х

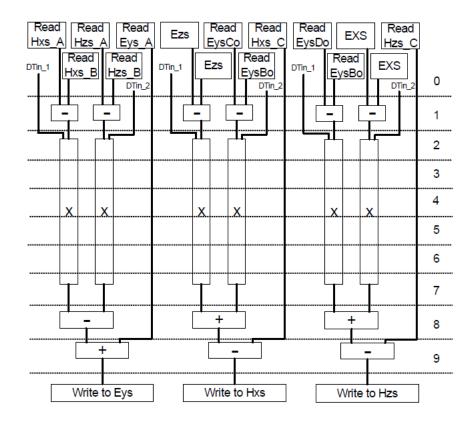

| FIGURE 4.14: | Version 2.0: 2D-FDTD 'H' field updating hardware design [4]                                                                              | 49 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|----|

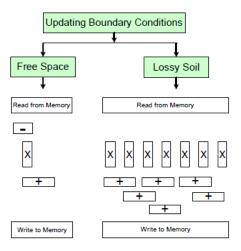

| FIGURE 4.15: | Version 2.0: 2D-FDTD boundary updating hardware design [4]                                                                               | 49 |

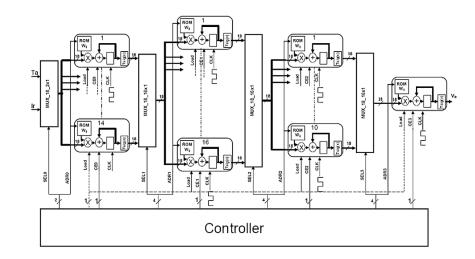

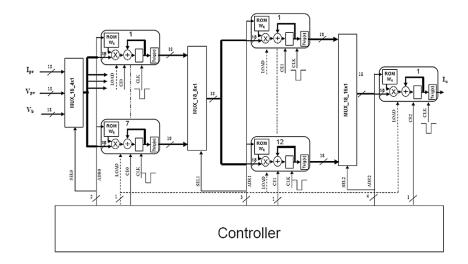

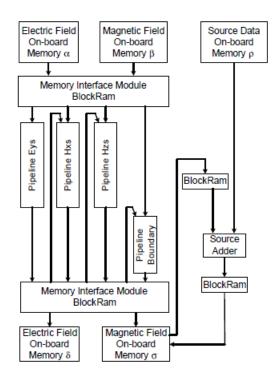

| FIGURE 4.16: | Version 2.0: 2D-FDTD overall hardware design [4]                                                                                         | 50 |

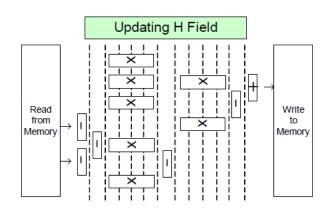

| FIGURE 4.17: | Version 3.0: 2D-FDTD UPML hardware design [5]                                                                                            | 51 |

| FIGURE 4.18: | Version 3.0: 2D-FDTD UPML hardware design [5]                                                                                            | 51 |

| FIGURE 4.19: | Version 3.0: 2D-FDTD UPML overall hardware design [5]                                                                                    | 52 |

| FIGURE 4.20: | Sparse Matrix-Vector multiplication hardware design versions                                                                             | 53 |

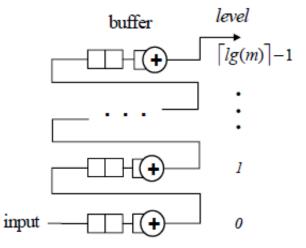

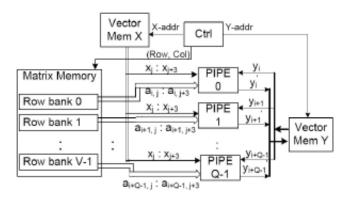

| FIGURE 4.21: | Version 1.0: SpMV multiply hardware [6]                                                                                                  | 54 |

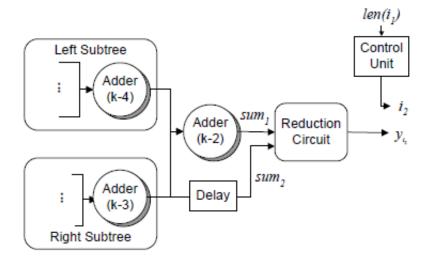

| FIGURE 4.22: | Version 1.0: SpMV reduction hardware [6]                                                                                                 | 54 |

| FIGURE 4.23: | Version 2.0: SpMV multiply hardware [7]                                                                                                  | 55 |

| FIGURE 4.24: | Version 2.0: SpMV reduction hardware [7]                                                                                                 | 56 |

| FIGURE 4.25: | Version 3.0: SpMV multiply hardware [8]                                                                                                  | 57 |

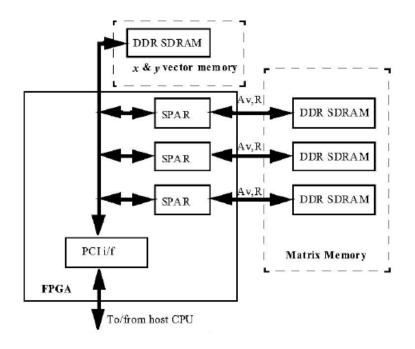

| FIGURE 4.26: | Version 3.0: SpMV overall hardware [8]                                                                                                   | 57 |

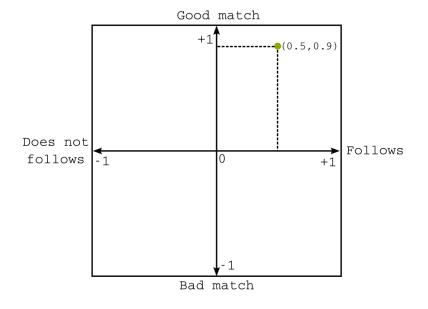

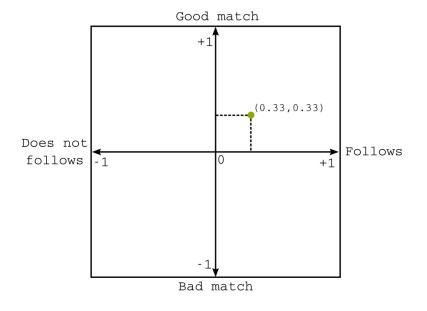

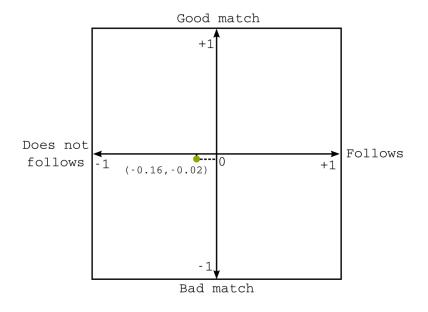

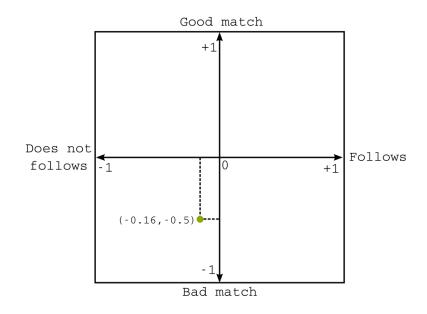

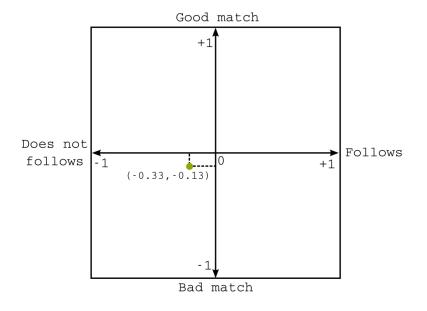

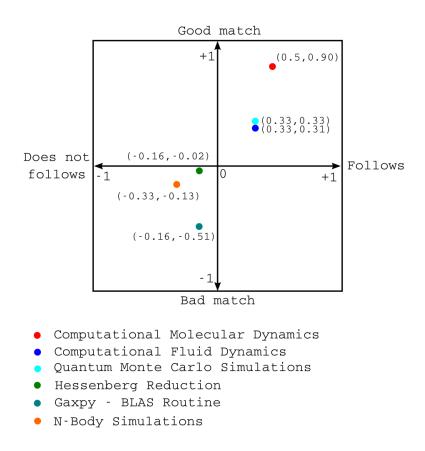

| FIGURE 4.27: | Guideline fitness plot                                                                                                                   | 60 |

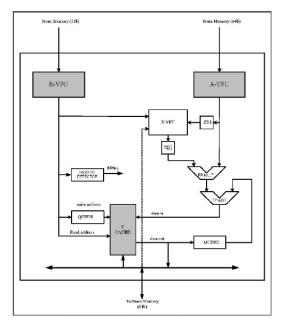

| FIGURE 4.28: | Computational fluid dynamics design [9]                                                                                                  | 61 |

| FIGURE 4.29: | Guideline fitness plot for CFD application                                                                                               | 62 |

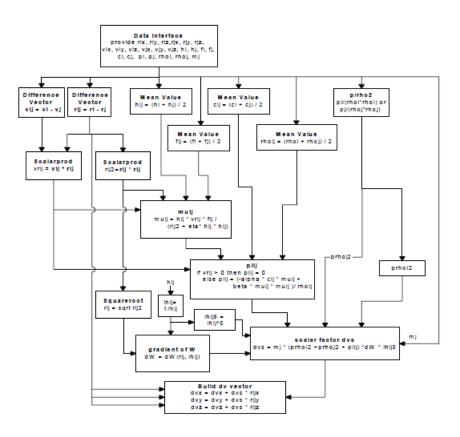

| FIGURE 4.30: | Molecular dynamics design [10]                                                                                                           | 64 |

| FIGURE 4.31: | Quantum Monte Carlo simulation design [11]                                                                                               | 65 |

| FIGURE 4.32: | Hessenberg reduction design [12]                                                                                                         | 66 |

| FIGURE 4.33: | Gaxpy Routine Design [13]                                                                                                                | 66 |

| FIGURE 4.34: | N-body hardware design [14]                                                                                                              | 68 |

| FIGURE 4.35: | $\Delta {\rm LOC}$ measurements for LFHD and GFHD (fictitious data)                                                                      | 70 |

| FIGURE 4.36: | Resource utilization for LFHD and GFHD (fictitious data)                                                                                 | 70 |

| FIGURE 4.37: | Performance measurements for LFHD and GFHD (fictitious data) $% \left( {{\left[ {{\left[ {{\left[ {\left[ {{\left[ {{\left[ {{\left[ {{$ | 71 |

| FIGURE 5.1:  | Plot comparing lines of code changed for P-V application                                                                                 | 76 |

| FIGURE 5.2:  | Plot comparing resource utilization for P-V application                                                                                  | 76 |

| FIGURE 5.3:  | Plot comparing slice utilization for P-V application                                                                                     | 77 |

|              |                                                                                                                                          |    |

|              |                                                                   | xii |

|--------------|-------------------------------------------------------------------|-----|

| FIGURE 5.4:  | Plot comparing performance for P-V application                    | 77  |

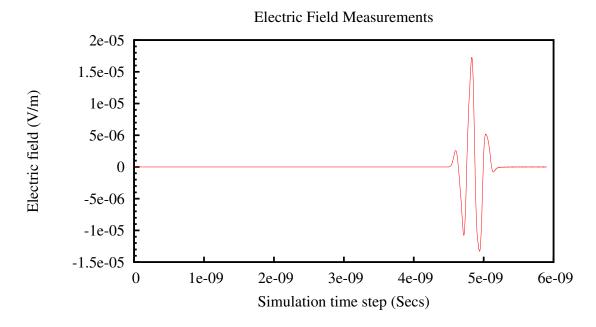

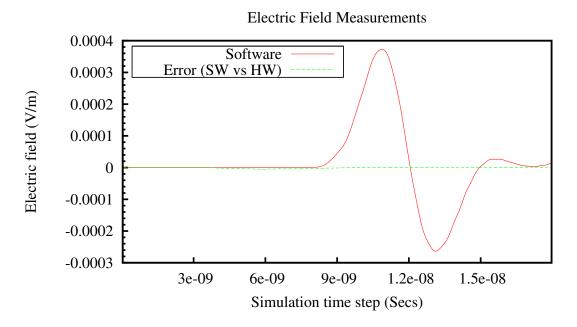

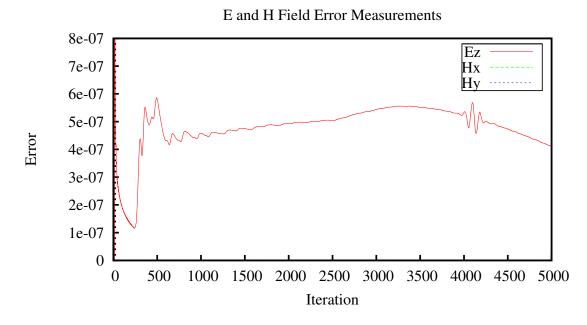

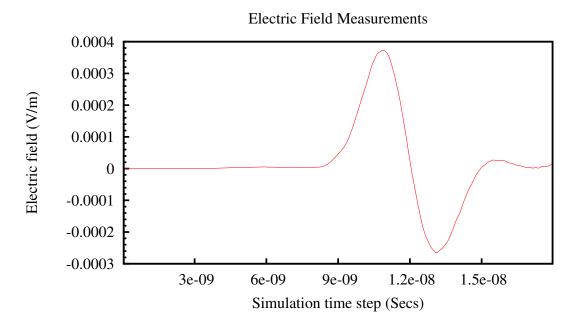

| FIGURE 5.5:  | Electric field at receiver port for 2D-FDTD PEC Model             | 79  |

| FIGURE 5.6:  | Electric field at receiver for 2D-FDTD LFHD PEC Model             | 80  |

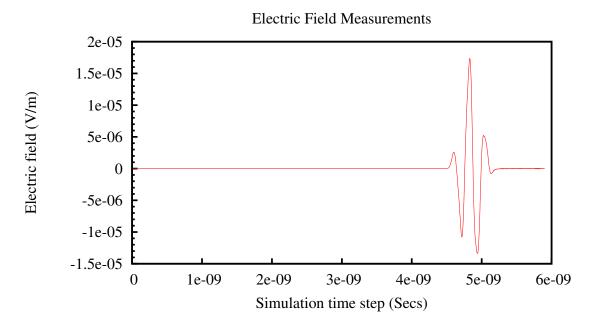

| FIGURE 5.7:  | Root mean square error value for $E$ and $H$ Fields for PEC model | 80  |

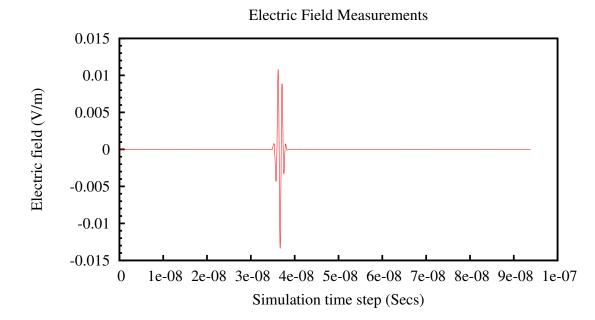

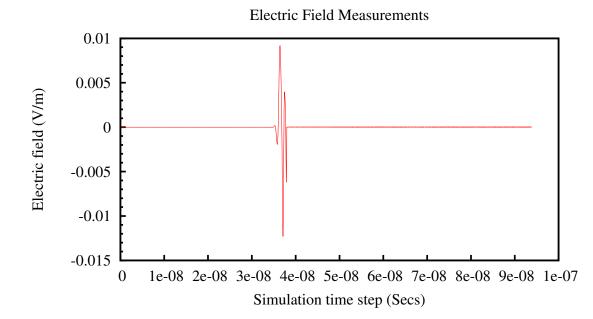

| FIGURE 5.8:  | Electric field at receiver port for 2D-FDTD Mur Model             | 81  |

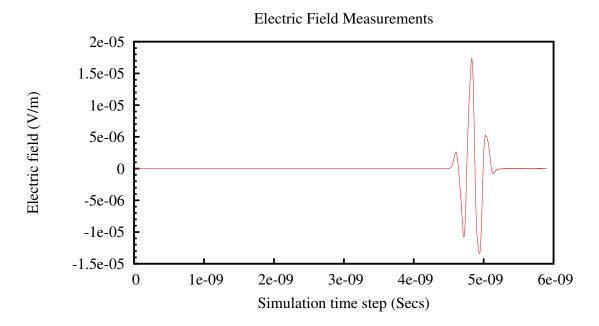

| FIGURE 5.9:  | Electric field at receiver port for 2D-FDTD UMPL Model            | 81  |

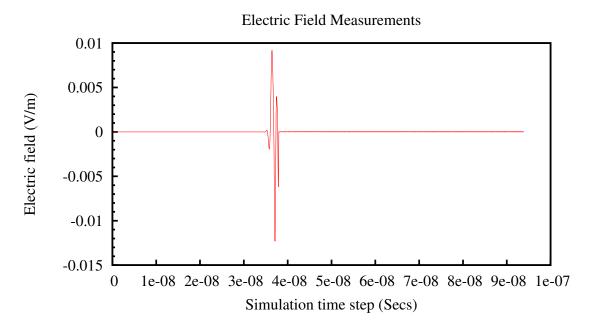

| FIGURE 5.10: | Electric field at receiver port for 2D-FDTD UMPL LFHD Model       | 82  |

| FIGURE 5.11: | Electric field at receiver port for 2D-FDTD GFHD PEC Model        | 83  |

| FIGURE 5.12: | RMSE values for $E$ and $H$ Fields for GFHD PEC model             | 83  |

| FIGURE 5.13: | Electric field at receiver port for 2D-FDTD Mur GFHD Model        | 84  |

| FIGURE 5.14: | Electric field at receiver port for 2D-FDTD UMPL GFHD Model       | 84  |

| FIGURE 5.15: | Plot comparing lines of code changed for FDTD                     | 86  |

| FIGURE 5.16: | Plot comparing resource utilization for FDTD                      | 86  |

| FIGURE 5.17: | Plot comparing slice resource utilization for FDTD                | 87  |

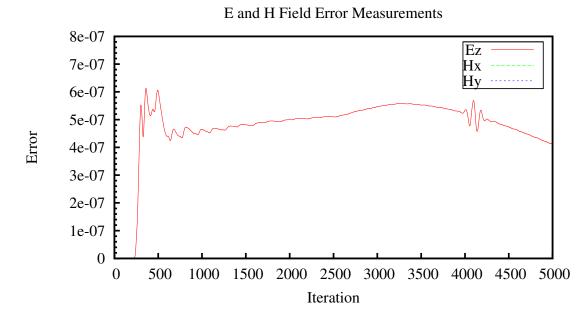

| FIGURE 5.18: | Plot comparing performance for FDTD                               | 87  |

| FIGURE 5.19: | Plot comparing lines of code changed for SpMV operation           | 93  |

| FIGURE 5.20: | Plot comparing resource utilization for SpMV operation            | 94  |

| FIGURE 5.21: | Plot comparing resource utilization for SpMV operation            | 94  |

| FIGURE 5.22: | Plot comparing performance for SpMV operation                     | 95  |

| FIGURE 5.23: | Guideline fitness plot for CFD application                        | 98  |

| FIGURE 5.24: | Guideline fitness plot for molecular dynamics application         | 99  |

| FIGURE 5.25: | Guideline fitness plot for quantum Monte Carlo simulations        | 100 |

| FIGURE 5.26: | Guideline fitness plot for Hessenberg Reduction                   | 102 |

| FIGURE 5.27: | Guideline fitness plot for Gaxpy - BLAS Routine                   | 104 |

| FIGURE 5.28: | Guideline fitness plot for N-Body Simulations                     | 105 |

| FIGURE 5.29: | Combined fitness plots for above six applications                 | 106 |

|              |                                                                   |     |

# LIST OF ABBREVIATIONS

| FPGA                  | field programmable gate array       |

|-----------------------|-------------------------------------|

| LFHD                  | literature followed hardware design |

| GFHD                  | guideline followed hardware design  |

| HW                    | hardware design                     |

| P-V                   | photo voltaic                       |

| NN                    | neural networks                     |

| FDTD                  | finite-difference time domain       |

| $\operatorname{SpMV}$ | sparse matrix vector multiplication |

| UPML                  | uniaxial perfectly matched layer    |

| CFD                   | computational fluid dynamics        |

| MD                    | molecular dynamics                  |

| HR                    | hessenberg reduction                |

| GFLOPS                | giga floating-point operations      |

| DDR                   | double data rate                    |

|                       |                                     |

basic linear algebra subprograms

BLAS

## CHAPTER 1: INTRODUCTION

Computational science, or scientific computing, is a field of study where scientists and engineers study the physical world by modeling it with computer simulations [15]. These simulations have led many to consider it a third branch of science<sup>1</sup>, along with the experimental and theoretical branches. Scientists greatly depend on simulation experiments because frequently the equivalent experiments in the physical world are either not possible or are prohibitively expensive. For example, there is no way to recreate the "big bang" but computer simulations can provide insight. Likewise, many drugs can be synthesized in the lab. However, each requires the development of process which can take months of work. Computer simulations offer the ability to sort through numerous candidates, reducing the search space to the most encouraging ones.

### 1.1 Computer Simulations

Some examples of computer simulation of the physical world include molecular dynamics, computational fluid dynamics, and electrodynamics simulations. In some cases, such as electrodynamics simulations, the real world is modeled using a set of mathematical equations and are solved in a discrete time domain [17]. Sometimes the equations are simplified models of the physical world; in other cases they come from first principles of physics. This makes solving these mathematical equations analytically impractical because it is tedious and time-consuming. Computer simulations make the process simpler and faster by solving the equations numerically with computer programs [18].

$<sup>^{1}</sup>$ A Google search for "third branch of science" results in numerous blogs, articles [16], and web pages discussing the topic.

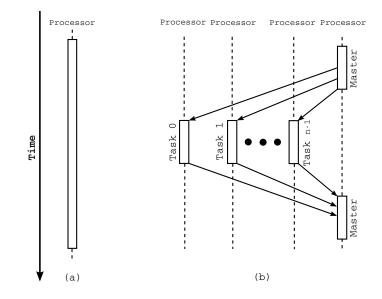

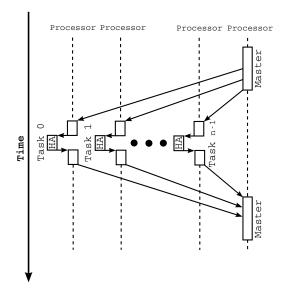

Figure 1.1: Sequential and parallel tasks

As the use of computers to study the behavior of the physical world has increased, scientists have become interested in capturing even more of the behavior of the physical world. This increases the complexity of the equations, resulting in longer simulation times. In order to reduce the time of these simulations, most computational scientists have relied upon computer engineers to produce ever-faster single processor machines. Unfortunately, for a number of technological reasons, single processor performance is not likely to continue to improve at the same rate as in the past [19]. This is forcing more computational scientists who want faster simulations to rely on parallel processing using parallel machines [20]. Instead of a single processor, parallel machines use multiple processors concurrently. This can be visualized in Figure 1.1 (time advances down the figure): (a) illustrates a single processor while (b) shows a collection of processors executing tasks concurrently. It also means more complicated parallel architectures because each processor has parallel cores.

In parallel processing, computational scientists divide their simulation experiments into smaller, independent tasks and execute their tasks concurrently (Figure 1.1b). These tasks are run on several processors simultaneously. In applications that scale well, computational scientists can use more processors in parallel to improve the performance and reduce the computation time.

As more and more parallel processors are used to improve the performance of applications, the communication between tasks, components utilized, space, and power requirements are increasing [21]. The increase in the power requirements also increases the cooling requirements. To reduce these growing requirements due to computing using parallel processors, and to increase performance per watt, computational scientist are always looking for alternative ways.

## 1.2 Hardware Accelerators

One of the active research areas to improve the performance per watt of a computational science application is the use of special-purpose hardware accelerators [22, 23]. These hardware accelerators have shown to improve the performance per watt of ordinary applications [24, 25, 26]. For example, graphic processor units (GPUs) are used to accelerate the construction of images in a frame buffer. The improvement in performance per watt of ordinary applications using hardware accelerators have motivated researchers and computational scientists to explore using these accelerators for their applications [27, 28, 29, 30, 31]. Similarly, most supercomputers in (1 - 5) of Top 500 list are built using hardware accelerators [32, 33]. Thus, the use of hardware accelerators improves performance per watt and reduces the run time of the application. That is, given a power constraint, hardware accelerators improves the performance of the application.

Presently, hardware accelerators for scientific applications are built either using Application-Specific Integrated Circuits (ASICs) [29, 34], Graphic Processor Units (GPUs) [35, 36], Cell/B.E. [27, 30, 37], Intel's Many Integrated Core (MIC) [38, 39], or Field Programmable Gate Arrays (FPGAs) [40, 41, 11]. The choice of ASIC, GPU, Cell, Intel's MIC, or FPGA-based hardware accelerator will depend on the application, the availability of hardware, and the developer's interests. However, as a practical matter we only consider FPGA devices in this work. An FPGA is an integrated circuit that has programmable logic and can be configured by the end user to perform special-purpose operations. A complete description is provided in Chapter 2.

A single node FPGA accelerator consists of a single FPGA-based hardware accelerator connected to the main (host) system via a system bus. However, in most cases a tighter coupling is required with the host system. Presently, the Peripheral Component Interconnect (PCI) bus and CPU socket plug-in boards configurations are used to achieve the coupling with the host system [22].

Once the computational scientists can justify the use of an single node FPGAbased hardware accelerator and build hardware designs for their application, then they can improve the performance per watt of their application by employing multiple FPGA-based accelerator nodes running in parallel, as shown in Figure 1.2. These multiple FPGA nodes could be connected using an interconnect. Such nodes connected together to form a single entity is referred to as an FPGA cluster. An example of such an FPGA cluster is the Spirit reconfigurable computing cluster built at Reconfigurable Computing Systems (RCS) Lab, University of North Carolina at Charlotte [42]. This type of parallel computing with multiple FPGA nodes and host processors is called as hybrid or heterogeneous high-performance computing [43, 44]. For the purpose of evaluation, only a single node of the Spirit cluster will be used. The ideas and concepts presented in this dissertation can be extended to an FPGA cluster.

As the computational scientists build better systems with hardware accelerators to simulate the behavior of the physical world, the performance per watt improves, and thus the run time of the simulation experiment decreases. For example, case studies such as molecular dynamics [10], finite difference time domain (FDTD) [45], and acceleration of quantum Monte Carlo simulations [11] shows a performance per

HA - Hardware Accelerator

Figure 1.2: Computing using hardware accelerators

watt improvement using an FPGA-based accelerator. The performance per watt improvement of the applications aids computational scientists to increase the fidelity of their simulation or are interested in capturing more behavior of the physical world. These increases lead to an understanding of the changes needed in the next experiments. These additions in successive experiments evolves the application code. As the application code evolves, the hardware engineers refactor the application code into serial and accelerator code. This refactoring of the application code introduces a huge cost for the accelerator design.

1.3 Cost of Refactoring

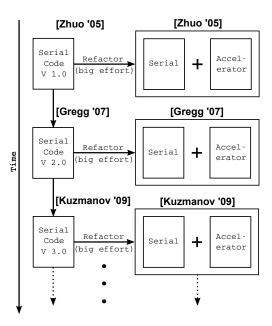

We define a *living* computational science application as an application whose source code evolves over time, as computational scientists increase the fidelity of their simulation or reduce execution time or wish to explore new phenomena. However, once the changes or additions are incorporated in the application code, the next major step would be to run these application codes on an FPGA-based hardware accelerator. In order to run these new application codes, the hardware engineer

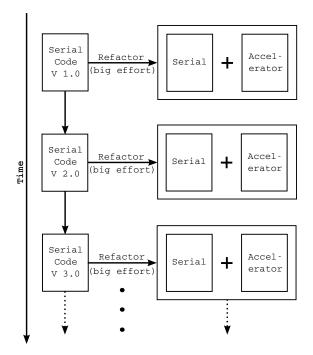

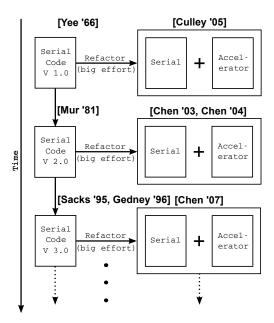

Figure 1.3: Human effort over time due code evolution

needs to refactor the application code into software and hardware sections. These hardware code sections are computed using an accelerator. As more phenomena are discovered, there are more revisions of the application code. Every revision of the application code introduces a new refactoring followed by a hardware redesign. Figure 1.3 illustrates this evolution of the source code over time. The critical point is that each time the code is revised (for example, going from version 1.0 to version 2.0), the serial application has to be refactored.

In a scenario where computational scientists are using FPGA-based hardware accelerator nodes in parallel to improve performance of their application, a small change in their application code introduces a refactoring of the application code. This refactoring forces the hardware engineer to re-design the hardware for every parallel node. As a result, a huge effort is required to re-build designs for an FPGAbased accelerator. This frequent design change considerably increase the wait time of the computational scientist to perform additional experiments, thereby reducing

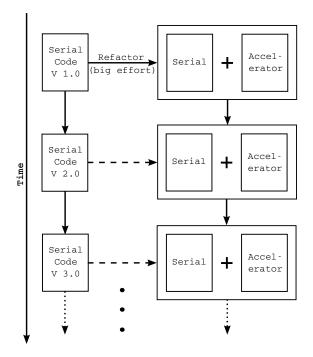

Figure 1.4: Key idea

their productivity.

Our hypothesis is that the frequent redesigns can be avoided by co-evolving the hardware design with the software. That is, as illustrated in Figure 1.4, only changes (or differences) from previous version is communicated, and the hardware is incrementally evolved or adapted. The overall effort is reduced by doing so, and productivity is improved. This key idea is not as simple as it sounds. However, we believe that if the hardware designers follow a set of design rules or guidelines for designing the initial hardware, the refactoring can be completely avoided, and performance and human effort can be preserved.

Thus, the thesis question we are trying to address is:—

Is there a set of hardware design guidelines for living computational science applications that can be easily communicated and is broadly applicable?

If the answer is affirmative, then the guidelines help designers efficiently accommodate the evolving changes in the living computational science application and achieve better performance and faster changes in the hardware design. If the answer is no, we have learned that these design guidelines cannot help designers efficiently accommodate the evolving changes. However, if these design guidelines are effective, then it could be used to formulate design guidelines for other hardware accelerator technologies.

As a computer engineer, we built hardware designs for several applications, such as exponential core design [46, 47], 3D-FDTD compute engine [48], N-body simulator [49], financial data feed handler [50], SpMV design [51], and Neural Network design [52]. In the process of building hardware designs for computational science applications, we realized that these applications could change. As we anticipated several design changes in these applications, we were motivated to formulate a set of design guidelines that could help the computer engineers or an FPGA specialist to co-evolve the hardware with the software. If this set of design guidelines is effective for living computational science codes for an FPGA accelerator, then these design guidelines can be used to experiment and formulate design guidelines for different accelerator technologies, such as GPUs, Cell/B.E, Intel's MIC, and ASICs.

## 1.4 Evaluation

To answer the thesis question, we propose a set of twelve design guidelines for hardware engineers to follow, with the expectation that it will help hardware designers to design hardware for living computational science applications. The set of design guidelines are then evaluated for its *effectiveness*, *communicability*, *and its broad applicability*. These design guidelines are simple and straight forward that fits in one page and are explained in 3.4. The guidelines can be easily understood and used by a hardware engineer to build FPGA hardware designs for living computational science applications. The set of twelve design guidelines are arranged in an order, so that, by following each guideline in the given order, they will help the hardware engineer to quickly understand the design guidelines and implement the hardware design. Thus, we argue that "easily communicated" is self-evident.

In order to evaluate the guidelines for effectiveness and its broad applicability, we will conduct two major experiments. The first experiment evaluates the design guidelines for its effectiveness using two applications and an operation from the literature. The second experiment evaluates the guidelines' broad applicability.

## 1.4.1 Experiment 1: Effectiveness

To evaluate the set of design guidelines for its effectiveness, two computational science applications and a computational science kernel is chosen from the literature. These applications are photo-voltaic (PV) system modeling and electromagnetic wave analysis using finite difference time domain (FDTD). The computational science kernel is sparse matrix-vector (SpMV) multiplication operation. This kernel is widely used in many computational science applications. These computational science applications are created by the computational scientists, and the hardware for these applications and the kernel are created by hardware engineers (FPGA specialist). Hence, these applications and the kernel are designed by a co-design team involving computational scientists and hardware engineers. A software version (version 1.0) of these applications and kernel exists (or will be recreated). The software version will capture the behavioral findings of the application and the kernel from the literature. Real datasets will be used to test the functionality of these applications and kernel. However, if real datasets are not available, synthetic data will be used, provided the performance of the application does not change. The software version 1.0 code of each application is reflactored into serial and accelerator code section, as shown in Figure 1.3. The accelerator code section is implemented on the accelerator referring to the literature, and this design is termed as *literature followed hardware* design (LFHD) or control group. These LFHD designs are derived from similar best designs that are existing in the literature. The accelerator code section of version 1.0 serial code is also built using the set of design guideline and is referred to as quideline

#### followed hardware design (GFHD) or experimental group.

Historical changes or additions from literature are introduced into version 1.0 software code to generate new versions (version 2.0, and 3.0) of software code. These historical changes or additions are chosen from the literature for respective applications and the kernel. These changes or additions are incorporated into the LFHD and into GFHD. Since these changes are historical, the hardware or the FPGA part used for their implementation could be old and outdated. As these FPGA parts are outdated, and cannot be used in the current computing platform, these LFHDs are to be designed and evaluated on a currently available FPGA (Virtex-4 FX60). In order to evaluate the designs effectively, and to maintain the fidelity of the designs, the architecture of the design, performance, and resource count has to be preserved when the LFHDs are built on a currently available Virtex-4 FX60 FPGA.

In order to preserve the architecture of the design, the design is reproduced to furthest extent possible on the Virtex-4 FX60 FPGA. The key point is that even though many of the older systems are not available, we are recreating the same environment. Similarly, to preserve the resource count, we constrain the design on Virtex-4 FX60 FPGA to recreate what was possible historically. In order to evaluate the designs effectively, the performance of the designs under evaluation (version 1.0, 2.0, and 3.0) needs to be preserved. Since the performance of an FPGA design mainly depends on the frequency of operation, the designs are operated at the reported frequency. Thus, the performance of the LFHDs are preserved, to maintain the fidelity of the design.

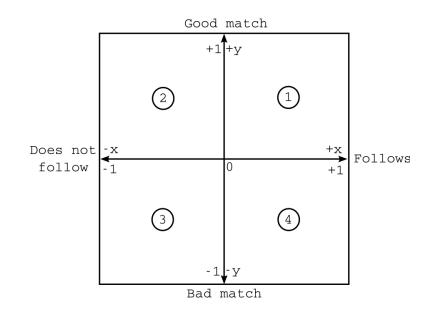

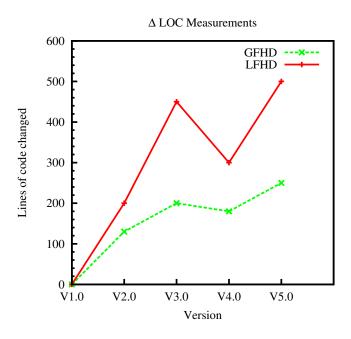

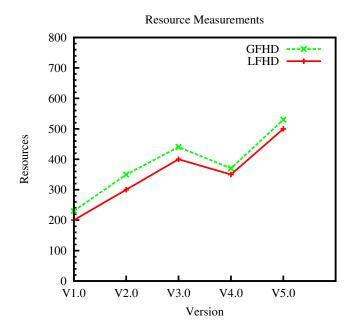

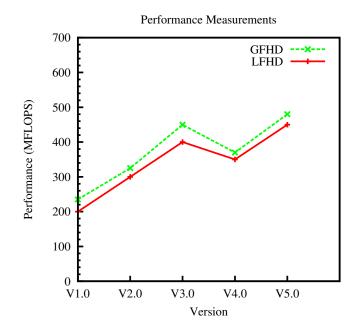

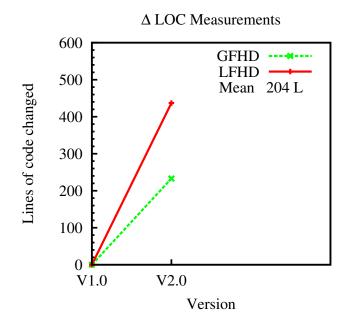

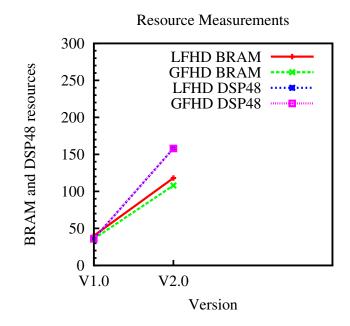

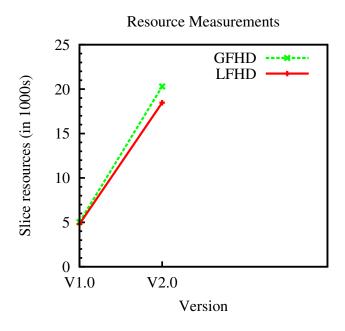

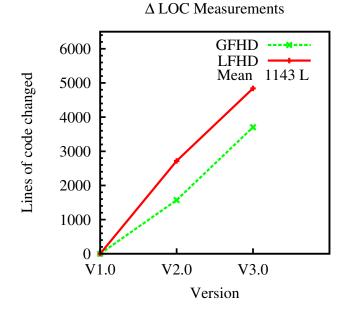

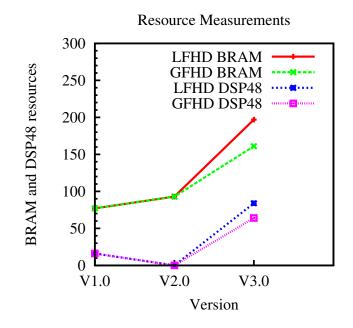

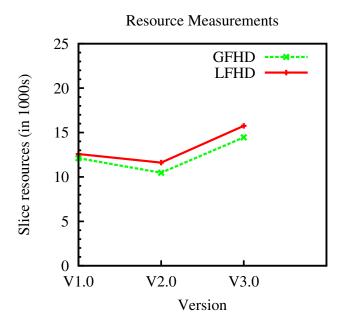

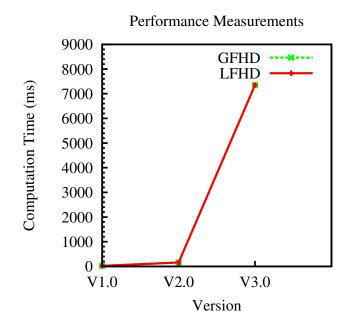

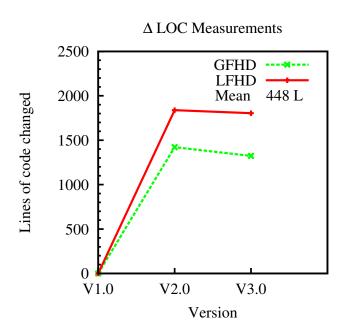

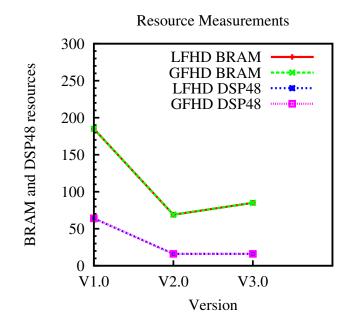

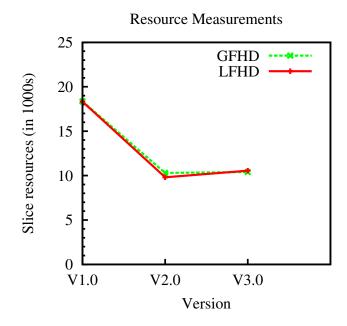

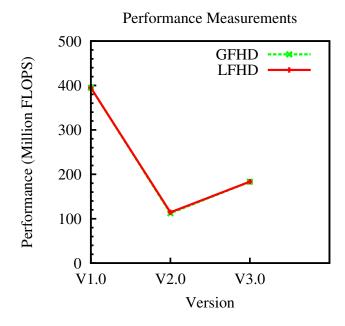

As the changes or additions from the literature is incorporated into the LFHD and into the GFHD, three key measurements are made. These measurements are (1) performance, (2) resource usage, and (3) lines of code changed and/or added ( $\Delta$ LOC). Lines of code changed is an approximate measure of effort involved in changing a hardware design. These measurements are tabulated and plotted, and comparisons are made, as shown in Figure 1.5. Plots are drawn for all the measurements comparing LFHD with GFHD (control group versus experimental group). The effectiveness of the design guidelines is measured by comparing the data points in the plots (performance, resource usage, and lines of code changed). If the data points for performance of GFHD and LFHD track each other with GFHD data points having higher or equal values, then the set of design guidelines is considered effective in terms of performance. That is, it is considered effective when the performance of guideline followed design (all versions) tracks the performance of literature design (all versions) as the scientific application changes (or new versions are created).

If the data points for resources of GFHD and LFHD track each other, then the set of design guidelines is considered effective in terms of resources. That is, as new versions of scientific code is created, if the resources used for guideline followed design is similar to the resources used for building literature followed design, then it is considered as effective in terms of resources. Similarly, if the data points for lines of code change for GFHD and LFHD diverge with GFHD data points having lower values, then the set of design guidelines is considered effective in terms of lines of code changed. When the data point diverge, there is large difference in the lines of code between literature design and guideline followed design to implement a change. That is, the effort involved in building guideline followed design is lesser than building literature followed design as the scientific application code changes.

If the performance and resource utilization data points for GFHD and LFHD track each other, and the lines of code diverge for GFHD and LFHD, then the degree of effectiveness is further used to affirm or deny the thesis question. On the contrary, if the performance and/or resource utilization data points do not track, and/or the lines of code data points do not diverge, then we can deny the thesis question.

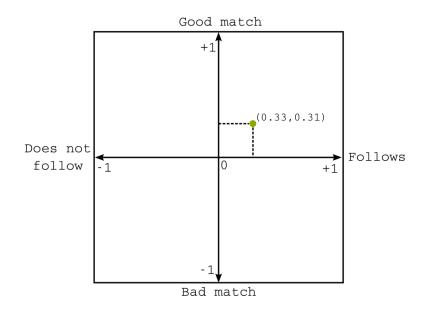

If the plots show effectiveness, the degree of effectiveness is then calculated by classifying the effectiveness into bad, good, and excellent. If the performance and

Figure 1.5: LFHD and GFHD evaluation

lines of code changed are classified as good or excellent, and the resources as bad or good or excellent for all the applications and the kernel, then we can ascertain that the set of guideline helps designers to effectively accommodate the evolving changes in the living computational science application. On the other hand, if the performance and lines of code changed are classified as bad, then the set of guidelines does not effectively accommodate the evolving changes in the living computational science application.

### 1.4.2 Experiment 2: Broad Applicability

To answer the question of broad applicability, besides the applications and kernel, a set of six applications are drawn from the literature and are evaluated using the set of guidelines. A guideline fitness plot is introduced to relate the number of guidelines followed to the performance of the application. The guideline fitness plot is plotted for each application, and each of these plots are combined to show the trend of application's performance with respect to the guidelines.

In order to answer the thesis question, the design guidelines needs to be evaluated, and these evaluations are carried out on a hardware platform. To get a better understanding of the hardware platform, the readers can go through Chapter 2. This chapter also provides an insight of the various existing tools and practices for living computational science applications. Once the readers have a better understanding of the hardware platform and the existing practices, Chapter 3 gives the scope of the design guidelines, and the methodology to implement these guidelines. The evaluation and validation of these guidelines are carried out on two applications and a kernel, and is discussed in Chapter 4. The results are presented in Chapter 5 with the conclusion in Chapter 6.

## CHAPTER 2: BACKGROUND

The designs and experiments in this dissertation are performed using an FPGA hardware platform. This section gives a brief description of FPGAs.

2.1 Field-Programmable Gate Arrays

An FPGA is an integrated circuit that mainly consists of logic blocks and interconnects. As the name suggests, an FPGA is configured by the end-users and not by the manufacturer. This feature gives end-users the ability to configure the device according to their needs. The term configuration is defined as the process of configuring the logical blocks and connecting them in a desired fashion to achieve a desired logical function. The work related to the dissertation was done using a Xilinx Virtex 4 FPGA device. This section will give a brief idea of the major components of a Virtex 4 FPGA that are listed below:

- Configurable logic blocks (CLBs)

- Digital clock managers (DCMs)

- Block RAMs (BRAM)

- PPC 405 processor

- XtremeDSP tile

- Ethernet MAC

## 2.1.1 Configurable Logic Blocks

Configurable logic blocks (CLBs) are the main building blocks of the FPGA that are used to build sequential and combinational circuits. A CLB consists of four

Figure 2.1: Configurable logic blocks and slices of a Virtex 4 FPGA

interconnected slices, shown in Figure 2.1. These slices are grouped in pairs and named as SLICEM and SLICEL. Both SLICEM and SLICEL have two look-up tables and two flip-flops. The SLICEM group has a distributed RAM and a 16-bit shift register. These SLICEL group can only be used for logic, however, SLICEM can be used to store a 64-bit word. The look-up table is a 4-input look-up table, and it is used to realize the digital logic functions.

### 2.1.2 Digital Clock Managers

The digital clock manager (DCM) generates clock signals for various modules in the FPGA. They provide a wide range of functions. It has a delay-locked loop (DLL) to eliminate clock delays, and it has features for doubling the clock and dividing the clock according to the requirements of the design. The DCM can also generate a phase-shifted clock that is required for designs and for interacting with the main memory.

#### 2.1.3 Block RAMs

Block RAMs are used for on-chip storage. Each block RAM can store up to 18 Kbits of data. Writes and reads are synchronous to the clock. The data in the block RAM can be accessed using two ports that can be used for writing or reading. The block RAMs can be combined to form any wide or any deep memory blocks. For some combinations of block RAM, a small amount of fabric logic may be used.

## 2.1.4 PPC 405 Processor

The PowerPC (PPC) processor core is a hardware IP in the Virtex 4 FX series FPGA. The PPC405 can work at a maximum frequency of 400 MHz. The PPC 405 processor can interface the user-defined cores through the processor local bus (PLB). It is a 32-bit address and 64-bit data bus. The PPC 405 can also interface using the device control register (DCR) and the on-chip memory (OCM) controller interface. The DCR helps in interfacing on-chip registers for device control. The OCM helps in adding more main memory to the processor. A joint action test group (JTAG) port is also provided to facilitate debugging of the software code running on the processor. The PPC 405 has an auxiliary processor unit (APU) that helps the designer to extend the PPC 405 instruction set. An instruction that is issued, is decoded both by the processor unit and by the APU. If the processor unit is able to generate the control signals, then the instruction is executed. However, if the APU recognizes the instruction, then the operands are forwarded to the fabric co-processor module (FCM). The FCM then computes on the operands, and the results are written back to the processor's registers for a write back. The complete process is shown in Figure 2.2

## 2.1.5 XtremeDSP Tile

Each XtremeDSP tile in a Virtex 4 FPGA device has two DSP48 slices. A DSP48 slice can support many functions, such as multiplication, multiplication-accumulation (MACC), multiplication followed by addition, three input addition, barrel shift-

Figure 2.2: PPC, APU, and FCM interaction

ing, and magnitude comparison. Each DSP48 slice has a 18-bit×18-bit 2's complement multiplier followed by a 48-bit signed adder/subtractor/accumulator. Each XteremeDSP can be cascaded without the use of fabric logic. The XteremeDSP tile can be used for building floating-point operations, such as addition and multiplication. Since these XtremeDSP tiles are hardware IP, their operating speeds are high.

## 2.1.6 Ethernet MAC Block

The Virtex 4 FPGA Ethernet Block contains two Ethernet MACs. Each Ethernet MAC supports 10/100/1000 Mbps data rates. Each Ethernet MAC has an address filter to accept or reject packets. The Ethernet block has a clock management module that configures the output clock frequency according to the Ethernet MAC speed setting and the mode settings.

As the scientific application code grows or changes, it becomes difficult and time consuming to build hardware designs using hardware description languages (HDLs). These factors motivated researchers, scientists, and companies to build C-to-HDL conversion tools and formulate design methodologies for FPGA designs.

#### 2.2 Related

## 2.2.1 Hardware/Software Co-Design

For many years hardware engineers are building designs with hardware and software components. A huge time and effort is required to design a system with hardware and software components. Moreover, a large design problem makes it unlikely for human designers to optimize all the objectives of the design. In order to meet and optimize the system level objectives, hardware and software are designed concurrently through hardware/software co-design [53]. This co-design methodology is generally applied to embedded system designs, system on chip designs, and others with rapid prototyping requirements. Computational scientists and hardware engineers can take advantage of hardware/software co-design methodology to design hardware for computational science applications. However, a change or additions in the code due to improving the fidelity of experiments or reducing the execution time or exploring new phenomena could result in introducing a new cycle of hardware/software co-design. 2.2.2 Scientific Application Design Methodologies

The work by Herbordt et al. [41] discusses a set of design methodologies for high performance reconfigurable computing (HPRC) applications. This work lists a set of twelve methods to improve performance of non-trivial HPRC applications. The work uses computational biology and molecular dynamics application as a case study for developing the design methods. Some of the key methods discussed are application restructuring, design and implementation, arithmetic operations, and integration issues. The work discusses general methods involved in improving throughput and performance of HPRC applications; however, it does not discuss design methodologies for code changes in living computational science applications.

#### 2.2.3 HDL Coding and Design Guidelines

There are many manuals and techniques to code a hardware description language (HDL). These are published in various books [54], articles, and websites. The set of design guidelines are complementary to the existing HDL coding guidelines. Similarly, there are many design techniques and guidelines for building FPGA-based hardware design, and these set of design guidelines are followed in addition to the existing HDL design techniques. These set of design guidelines augment specifically living computational science applications.

## 2.2.4 C-to-HDL Conversion Tools

C-to-HDL conversion tools converts C or C-like code to a HDL. The converted code can then be synthesized to configure an FPGA. The conversion tools help to overcome the issues related to application growth and changes in functionality of a scientific computing application. Over the past two decades, there has been a continuous effort made by different companies and researchers to build C-to-HDL conversion tools. A few of them are listed below, and their advantages and disadvantages are also listed.

SystemC [55] was an effort made by an open systemC initiative (OSCI) that is an open source extension of C++ for hardware/software co-design. The syntax of SystemC is a mix of C++ and VHSIC hardware description language (VHDL). One of the major advantage of SystemC is that the programmer can co-design and co-simulate a system. The drawback of SystemC is that it does not generate synthesizable HDL. However, a two step process is required to generate synthesizable HDL.SystemC is system-level modeling language. However, there has been lot of effort [56] to generate hardware synthesizable code and to generate transparency in the algorithm, which exposes the relationship between inputs and outputs.

Handel-C [57] is a high level programming language from Celoxica. Handel-C uses C-like constructs for inherent parallelism. The communication between parallel blocks is done using channels or first-in first-out (FIFO) hardware. Handel-C

does not support floating-point operations; however, library calls can be made for floating-point operations. An interface construct is used to communicate with external devices and external logic. Every interface construct has port definitions for communication. Handel-C supports pointers and pointer-to-functions and it code can also be simulated.

Dime-C was developed by Nallatech [58] and generates VHDL that can be portmapped into other hardware designs. It supports American National Standards Institute (ANSI) C constructs; however, some special constructs help in optimizing the output VHDL code and support floating-point operations. The resources are shared between parallel processes, and it automatically optimizes code for parallel and pipeline implementation. Dime-C designs can be simulated, and, whenever possible, Dime-C uses DSP48 slices instead of fabric logic for IP cores. It can create two reads/writes or one read/write interface for the BRAM blocks. The major disadvantage of Dime-C is that it does not create optimized HDL[59].

ImpulseC was developed by Impluse Accelerated Technologies [60]. Impulse CoDeveloper is the integrated development environment (IDE) used for coding and simulation. This IDE includes ImpulseC, interactive parallel optimizer, and platform support packages (PSP) that can be configured for a wide range of FPGA-based computing systems. PSPs specify the type of FPGA on the board and how Impulse CoDeveloper can convert the code for that particular FPGA. A PSP is created to configure Impulse CoDeveloper for a specific FPGA board. Once Impulse CoDeveloper is configured through a PSP for a particular FPGA board, the end-user can write C code to design systems. The designs built using ImpulseC can be partitioned into software and hardware blocks. The software block runs on the processor of the FPGA, and the hardware block is converted into HDL to be synthesized. The user can transfer data between software and hardware blocks using *co\_streams, co\_registers, and co\_signals.* Co\_streams are FIFOs, co\_registers are registered signals and co\_ signals are used for handshaking and interrupts. The user can design systems completely that are written in ImpulseC or can design using VHDL and Impulse C. In cases where the designs are mixed (i.e., VHDL and Impulse C), the user can interface the ImpulseC system using co\_streams and co\_registers to the VHDL design.

Although C-to-HDL tools help hardware engineers to build deigns for FPGA, some of these tools don't support floating-point, some of them are used for simulation, and most of them do not generate resource optimized HDL. Some of C-to-HDL tools do not allow fine-grain control of the built hardware [61]. As computational scientist improve the fidelity of the code or reduce execution time or wish to explore new phenomena, the code changes or grows. As these scientific code grows, additional FPGA resources may be required. If C-to-HDL tools are used to build designs for growing computational science codes, these designs could use more resources when compared to designs built using VHDL.

The next section discusses scope and methodology for the thesis question we are trying to answer.

## CHAPTER 3: SCOPE AND METHODOLOGY

As scientists try to simulate real world problems, their application code will continue to change overtime due to two facts: a new discovery lead to new questions and a desire to study new phenomena. If the scientists use a hardware accelerator to increase the rate of execution, then every new version would require substantial effort to accomplish the changes in the accelerator code. In this work, we assume that the accelerator is an FPGA device, and the following sections discuss the key idea, scope of the work, pre-design, and hardware design for living scientific applications.

#### 3.1 Key Idea

Using a hardware accelerator core poses a real disadvantage to scientists whose scientific code is changing or evolving over time. Whenever, there is a change in the code, a refactoring is required. Every refactoring causes a computer engineer to inspect the source code and create accelerator-specific code plus some sequential code. This process is illustrated by the graphic originally shown in Chapter 1 and reproduced in Figure 3.1. In order to reduce the effort of refactoring, the hypothesis of this thesis is that designs can be built such that there is minimum effort for incorporating the changes. The changes from the new code, and the previous version of sequential code and accelerator code, is used to generate a new version of sequential and accelerator code. The key idea is illustrated by the graphic reproduced in Figure 3.2. The dotted lines represent that only the changes are extracted, and the arrow from the previous serial and accelerator block shows that the previous version of serial and accelerator code is used for creating the new version of serial and accelerator code. The overall effort is reduced by doing so, and the productivity is also improved. In order to accomplish the key idea, the designers need to design the hardware in a cer-

Figure 3.1: Effort due code evolution

tain style. This dissertation offers hardware design for the above discussed hardware.Before discussing the design, the next section discusses the scope of the design/work.3.2 Scope of the Work

In order to answer the thesis question, the dissertation offers a set of design guidelines that, when followed, helps the hardware engineer to build designs that are effective when the design changes due to changes in the scientific application code. As discussed earlier, these design guidelines are applicable to FPGA designs that has shown consistent speed-up when compared to other hardware platforms used for scientific computing. This set of design guidelines is also specific for living computational science applications. In order to answer the thesis question, two applications and an operation are chosen from the literature, and the guidelines are evaluated for effectiveness, communicability, and broad applicability. These applications and the operation are built on a single-node FPGA, and the guidelines are evaluated using the single-node FPGA infrastructure. The next section gives a brief idea of analyzing the application code, and dividing the application code into serial and accelerator

Figure 3.2: Key idea

code.

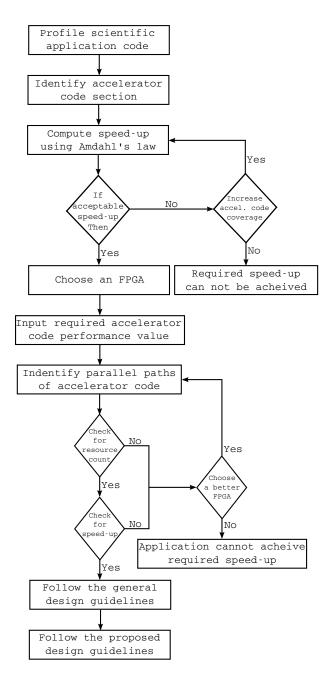

# 3.3 Analysis of Sequential Code

In order to speed-up a living scientific code, the code is profiled and analyzed, and the time consuming section/sections are identified, shown in Figure 3.3. One or more time consuming sections constitutes the accelerator code section. Once the accelerator section is identified, the number of parallel paths are identified, and the approximate time taken to marshal data between the software and hardware is calculated. With the number of parallel paths, marshaling time, and fraction of time spent (from profile information) in the accelerator code, an approximate speed-up is computed using Amdahl's law. The speed-up computed is just an approximate value as the actual value can be only calculated after the accelerator code is implemented using an FPGA. If the computed speed-up is not acceptable to the user, then the accelerator section coverage is increased so that the time spent in the section is increased. The increase in the coverage of the accelerator section is achieved by increasing the lines of code or by adding more time consuming sections. An approximate speed-up due to the new accelerator section is again computed using Amdahl's law.

Assuming the speed-up is achieved using several time consuming sections, the speed-up of an individual time consuming section is defined by equation 3.2:

$$\gamma = \frac{hardware \ speed}{software \ speed} = \frac{\frac{1}{hardware \ time}}{\frac{1}{software \ time}} = \frac{software \ time}{hardware \ time}$$

(3.1)

$$\gamma(i) = \frac{s(i)}{h(i) + m(i)} \tag{3.2}$$

Where h(i) and s(i) are the time spent in hardware and software sections, respectively, for the time consuming section *i*. The time spent to marshal data between the processor and the FPGA is m(i). Assuming that we use a single time consuming section to form the accelerator section, and knowing the fraction of time spent in a time consuming section (k(i)) from the profile information, we can calculate the overall speed-up using Amdahl's law. Amdahl's law states that if F is the fraction that can be enhanced and (1 - F) is the fraction that cannot be enhanced, then the maximum speed-up that can be achieved can be computed using equations 3.3 and 3.4. Rewriting equation 3.4 with time consuming section k(i) and its speed-up  $\gamma(i)$ results in equation 3.5.

$$Speedup_{overall} = \frac{1}{(1 - Fraction_{enhanced}) + \frac{Fraction_{enhanced}}{Speedup_{enhanced}}}$$

(3.3)

$$Speedup_{overall} = \frac{1}{(1 - F_{enhanced}) + \frac{F_{enhanced}}{Speedup_{enhanced}}}$$

(3.4)

$$\Gamma = \left[ (1 - k(i)) + \frac{k(i)}{\gamma(i)} \right]^{-1}$$

(3.5)

If the accelerator section consists of a set of time consuming sections  $\mathbb{D}$ , then the overall speed can calculated, as shown in equation 3.6.

$$\Gamma(\mathbb{D}) = \left[1 + \sum_{i \in \mathbb{D}} \left(\frac{k(i)}{\gamma(i)} - k(i)\right)\right]^{-1}$$

(3.6)

If the new speed-up is not acceptable, then the accelerator section coverage is again increased. This process is continued until an acceptable speed-up is achieved. If such a speed-up cannot be achieved, then the acceleration of the application is not possible. If the application can be sped-up using an accelerator, an FPGA part is selected. The accelerator section's parallel paths are identified, and it is then divided into small hardware blocks that could fit the FPGA. These hardware blocks are chosen in such a way that the blocks can be reused. If possible, the hardware blocks are pipelined. The hardware blocks could be a simple arithmetic operation or a compound operation.

Once the hardware design is decided, the resource count is calculated. If the total resource count is less than the FPGA resources, a speed-up computation is again performed using equations 3.4, 3.5, and 3.6. If a desired speed-up can be achieved, then the set of guidelines is followed. If the resource requirement is more than the FPGA resources, then a better FPGA is chosen, and the hardware blocks are again designed for the new FPGA. The next section gives a detailed example of a living computational science application hardware design.

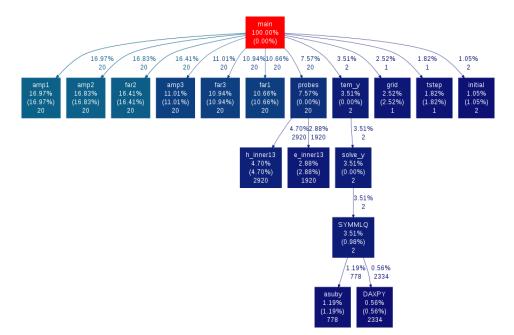

## 3.3.1 Example: Electrodynamics Application

For demonstration purposes, let us profile electrodynamics application for analyzing microstrip discontinuities (FDTD). The profile output is shown in Figure 3.4. The time consuming sections (kernel) of the application are amp1, amp2, amp3, far1, far2, and far3 subroutines. Let's compute the speed-up using equation 3.5. If the amp1 kernel is implemented on an FPGA accelerator, then the value of k(i) is 16.97%. Assuming we achieved a speed-up of 10x compared to the software using an FPGA accelerator, the overall speed-up is computed as 1.094x. However, if amp2, amp3, far1, far2, and far3 are also implemented on an FPGA accelerator with an average

Figure 3.3: Analysis and pre-design

speed-up of 10x compared to the software, then the overall speed-up is computed as 5.29x, using equation 3.6. The k(i) values for each kernel are shown in Figure 3.4.

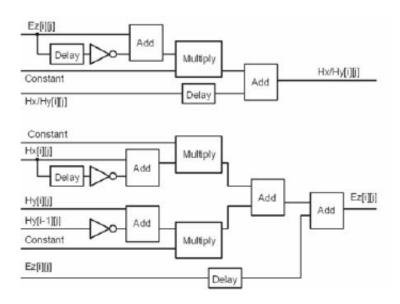

Figure 3.4: FDTD Profile Information

In this application, the material under experiment is spatially divided into small cubes (unit cells) along three dimensions. The problem is computing the magnetic and electric field in a leap frog fashion. In practice, the material is divided into a huge number (order of 100K) of tiny cubes (unit cells), and the computation is repeated 10,000 times over each unit cell. In order to perform the computation, the computational domain is chosen such that every computational sub-domain consists of thousands of similar unit cells. That is, the whole region under test is divided into smaller regions along one axis. Electromagnetic properties are then computed in parallel over these smaller regions to improve performance. As discussed above, the kernel is shown in equations 3.7 - 3.12, and it is broken down into smaller hardware blocks that can be reused. To build an efficient design for the FPGA, two important questions are to be addressed. The first question is the number of parallel cores and its dataset.

$$E_{x_{i,j,k}}^{n+1} = E_{x_{i,j,k}}^n + C_1 \left( H_{z_{i,j+1,k}}^{n+1/2} - H_{z_{i,j,k}}^{n+1/2} \right) + C_2 \left( H_{y_{i,j,k+1}}^{n+1/2} - H_{y_{i,j,k}}^{n+1/2} \right)$$

(3.7)

$$E_{y_{i,j,k}}^{n+1} = E_{y_{i,j,k}}^n + C_3 \left( H_{x_{i,j,k+1}}^{n+1/2} - H_{x_{i,j,k}}^{n+1/2} \right) + C_4 \left( H_{z_{i+1,j,k}}^{n+1/2} - H_{z_{i,j,k}}^{n+1/2} \right)$$

(3.8)

$$E_{z_{i,j,k}}^{n+1} = E_{z_{i,j,k}}^n + C_5 \left( H_{y_{i+1,j,k}}^{n+1/2} - H_{y_{i,j,k}}^{n+1/2} \right) + C_6 \left( H_{x_{i,j+1,k}}^{n+1/2} - H_{x_{i,j,k}}^{n+1/2} \right)$$

(3.9)

$$H_{x_{i,j,k}}^{n+1} = H_{x_{i,j,k}}^n + C_7 \left( E_{z_{i,j+1,k}}^{n+1/2} - E_{z_{i,j,k}}^{n+1/2} \right) + C_8 \left( E_{y_{i,j,k+1}}^{n+1/2} - E_{y_{i,j,k}}^{n+1/2} \right)$$

(3.10)

$$H_{y_{i,j,k}}^{n+1} = H_{y_{i,j,k}}^n + C_9 \left( E_{x_{i,j,k+1}}^{n+1/2} - E_{x_{i,j,k}}^{n+1/2} \right) + C_{10} \left( E_{z_{i+1,j,k}}^{n+1/2} - E_{z_{i,j,k}}^{n+1/2} \right)$$

(3.11)

$$H_{z_{i,j,k}}^{n+1} = H_{z_{i,j,k}}^n + C_{11} \left( E_{y_{i+1,j,k}}^{n+1/2} - E_{y_{i,j,k}}^{n+1/2} \right) + C_{12} \left( E_{x_{i,j+1,k}}^{n+1/2} - E_{x_{i,j,k}}^{n+1/2} \right)$$

(3.12)

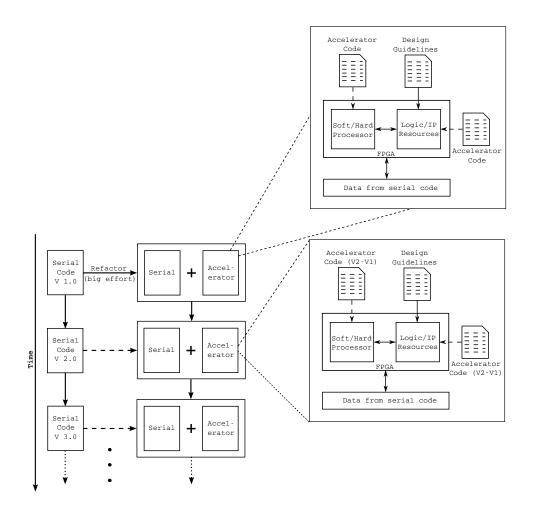

#### 3.4 Hardware Design

As scientists discover new phenomena of their application code, they incorporate these new findings in the code. If scientists have an accelerator to accelerate their code, it becomes more difficult to incorporate those changes into the accelerator code. As discussed in the key idea section, the goal is to come up with a hardware design that can handle these changes. The design of such a hardware is not as simple as it sounds. We believe that if the initial hardware is built following a set of design guidelines or rules as tabulated in Table 3.1, then the successive hardware changes due to application code changes which can be easily incorporated.

This set of design guidelines form the basis of this work. These design guidelines are followed when the hardware for the scientific application is designed. A high-level design is shown in Figure 3.5. As shown in the figure, the serial code is divided into serial and accelerator code. The accelerator code and the design guidelines are then used to build the hardware design. The accelerator code is also used to build the software code that runs on the processor of the FPGA. The main function of software code is to configure or to connect the various resources in the FPGA, according to the requirements of the application. The resources are chosen according to the initial version (version 1.0) of the application. As the application code or the

|             | Table 3.1. Debign Suldennes for nying compatational before appreations          |

|-------------|---------------------------------------------------------------------------------|

| 1           | Arrange and optimize input/output data for all compute blocks                   |

| 2           | Adhere to a widely accepted method of computation for arithmetic function-      |

|             | <i>s</i> /operations                                                            |

| 3           | Build controller for every not likely to change compute blocks                  |

| 4           | Introduce a configurable dataflow path to connect resources of likely to change |

|             | compute blocks                                                                  |

| 5           | Introduce on-chip memory with configurable read/write logic, if necessary       |

| 6           | Introduce dependency indicators to enhance parallel computations, if neces-     |

|             | sary                                                                            |

| $\tilde{7}$ | Use microcode to specify dataflow path, memory read/write, and parallel com-    |

|             | putations                                                                       |

| 8           | Maximize resource utilization by improving runtime parallelism                  |

| 9           | Forward results between compute blocks/resources, if possible                   |

| 10          | Achieve functionality, and optimize design & resources to improve perfor-       |

|             | mance                                                                           |

| 11          | Maximize computation until maximum memory bandwidth is utilized                 |

| 12          | Use a large and real dataset for test cases                                     |

|             |                                                                                 |

Table 3.1: Design guidelines for living computational science applications

serial code changes, the accelerator code also changes. These changes (or differences) are communicated to the next version of serial and accelerator code. The changed accelerator code is then used to build the new software code for the processor in the FPGA. The next section discusses the evaluation of the set of design guidelines and its validation.

Figure 3.5: Hardware design

## CHAPTER 4: EVALUATION AND VALIDATION

The set of design guidelines can be evaluated and validated by measuring the effort, performance changes, and resource usage as the hardware design evolves with the application. It is also required to evaluate the design guidelines for easy communicability and broad applicability. Hence, this section will discuss in detail about the various evaluations and their methods. To summarize, the key evaluations that will be performed in this section are:

- Effectiveness of design guideline

- Communicability of design guideline

- Broad applicability of design guideline

## 4.1 Effectiveness of design guideline

The set of design guidelines that is used to built hardware designs, can be evaluated by recording the lines of code added or changed, change in performance, if any, and resource utilization as the application evolves from one version to the next. These measurements are then compared to the recorded measurements of existing designs in the literature. For the sake of simplicity, the hardware design built using the set of design guidelines will be referred as *guideline followed hardware design (GFHD) or controlled group*. Similarly, the hardware design built from literature will be referred as *literature followed hardware design (LFHD) or experimental group*. The important part of the evaluation is to determine effectiveness of the set of design guidelines. To be more specific, the effectiveness of the design guideline is measured by finding the lines of code that is required to incorporate a change or addition in the hardware design due to new findings. By implementing these set of design guidelines, it is also important to measure whether there is any performance changes between the LFHD and the GFHD. The performance changes, if any, due to additions or changes in the application will also be recorded for both the LFHD and GFHD to give the hardware designers an idea of performance changes.

The hardware engineer who is following the set of guidelines would be interested to know whether there is any additional resource usage introduced by the set of design guidelines. To be specific, this dissertation is focused on FPGA designs, and the resource usage will be indicated as slices, DSP blocks, BRAM blocks. The resources used due to additions or changes in the application will also be recorded for both the LFHD and GFHD to give the hardware designer an idea of overhead, if any. To summarize, the key measurements that will be recorded to evaluate the effectiveness of the solution are:

- Performance

- Resource usage

- Lines of code added or changed

## 4.1.1 Design Guideline Evaluation Metrics

This dissertation offers a set of twelve guidelines, as shown in Table 4.1 for hardware engineers. It also shows the order in which the set of guidelines needs to be followed. This order has been established by considering the design path an FPGA designer would normally follow. A change in the order of the design guideline will introduce multiple design cycles. In order to evaluate the set of design guidelines, two computational science applications and a computational science kernel is chosen from the literature. These scientific applications are designed by computational scientists, and the hardware for the application and the kernel is designed by hardware engineers. Hence, these designs are team co-designs consisting of hardware engineer and computational scientists.

The applications are photo-voltaic (P-V) system modeling and electromagnetic wave analysis using finite difference time domain (FDTD). The computational science kernel is sparse matrix-vector multiplication (SpMV) operation. Photo-voltaic modeling and simulation application models the power generation of solar panels using neural networks (NNs). Software and hardware versions (1.0 and 2.0) of P-V generation model is created from the literature. The version 2.0 model adds battery model and regulator model for overall P-V system performance. Electromagnetic wave analysis application uses FDTD method to compute electric and magnetic field values of a material under test. Software and hardware versions (1.0, 2.0, and 3.0) of electromagnetic wave analysis created from the literature consists of 2D transverse magnetic (TM) model of FDTD with different types of boundary conditions. Sparse matrix-vector multiplication operation provides optimized routines to compute multiplication of a large sparse matrix with a vector of values. Software and hardware version (1.0, 2.0, and 3.0) are created from the literature. Each version provides a better multiplication computation to reduce the overall execution time.

Each of the above application consists of three versions of software code. The software version (version 1.0) of these applications exists (or will be recreated) and will be tested with real datasets. The software version 1.0 code of each application is refactored into serial and accelerator code. The accelerator code is implemented on the accelerator, and is termed as literature followed hardware design (LFHD) or control group. These LFHD designs are derived from the existing designs in the literature. A GFHD is also built for the version 1.0 accelerator code and is termed as experimental group.

In order to introduce changes or additions into version 1.0 software code, historical changes from the literature is used. These changes to the version 1.0 code generates

| 1        | Arrange and optimize input/output data for all compute blocks                         |

|----------|---------------------------------------------------------------------------------------|

| 2        | Adhere to a widely accepted method of computation for arithmetic function-            |

|          | <i>s</i> /operations                                                                  |

| 3        | Build controller for every not likely to change compute blocks                        |

| 4        | Introduce a configurable dataflow path to connect resources of likely to change       |

|          | compute blocks                                                                        |

| 5        | Introduce on-chip memory with configurable read/write logic, if necessary             |

| 6        | Introduce dependency indicators to enhance parallel computations, if neces-           |

|          | sary                                                                                  |

| $\gamma$ | Use microcode to specify dataflow path, memory read/write, and parallel com-          |

|          | putations                                                                             |

| 8        | Maximize resource utilization by improving runtime parallelism                        |

| 9        | Forward results between compute blocks/resources, if possible                         |

| 10       | Achieve functionality, and optimize design $\mathcal{C}$ resources to improve perfor- |

|          | mance                                                                                 |

| 11       | Maximize computation until maximum memory bandwidth is utilized                       |

| 12       | Use a large and real dataset for test cases                                           |

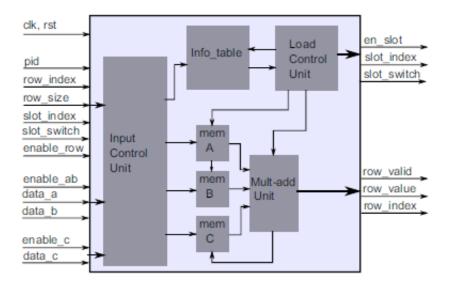

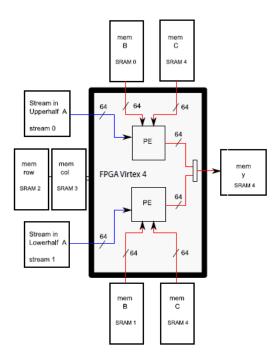

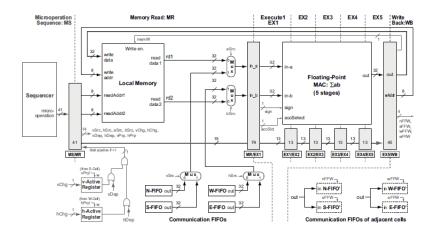

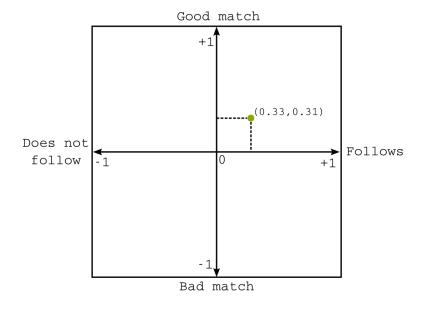

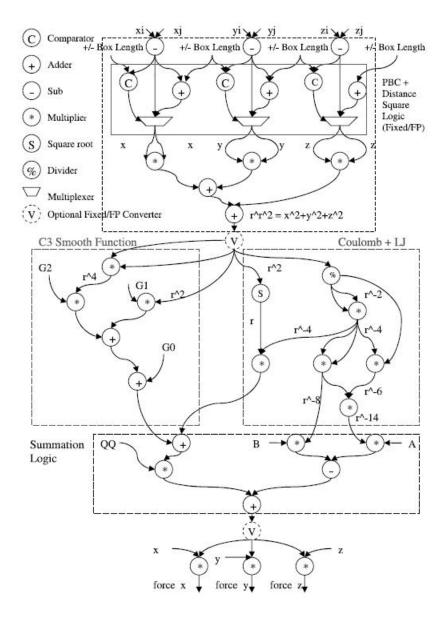

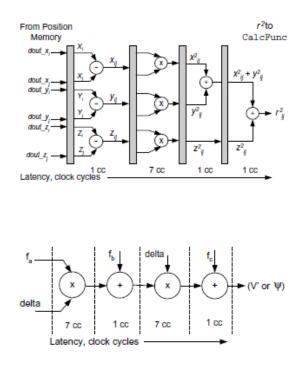

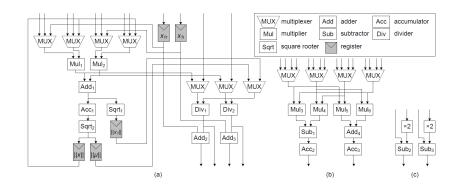

Table 4.1: Design guidelines for living computational science applications